- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373975 > ADATE207BBPZ (ANALOG DEVICES INC) Quad Pin Timing Formatter PDF資料下載

參數(shù)資料

| 型號(hào): | ADATE207BBPZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類(lèi): | 消費(fèi)家電 |

| 英文描述: | Quad Pin Timing Formatter |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PBGA256 |

| 封裝: | ROHS COMPLIANT, MO-192-BAL-2, LBGA-256 |

| 文件頁(yè)數(shù): | 32/36頁(yè) |

| 文件大小: | 374K |

| 代理商: | ADATE207BBPZ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

ADATE207

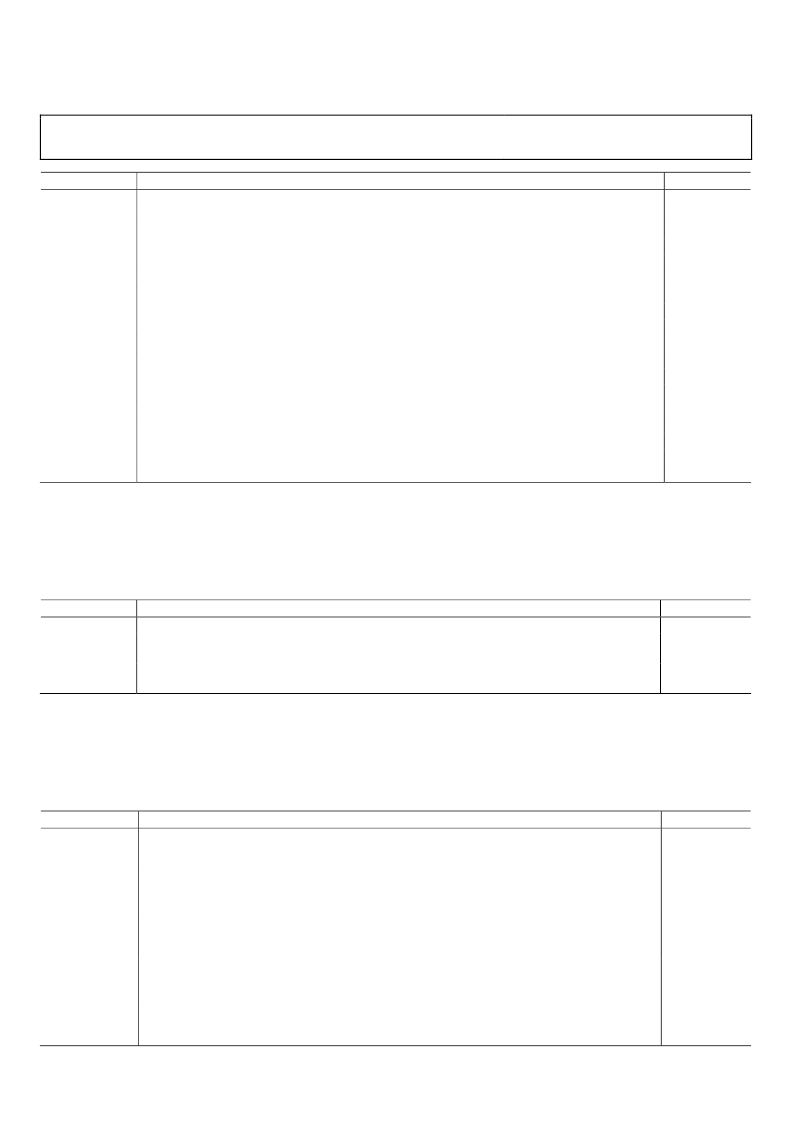

Position

Bit 03

Bits[02:00]

Rev. 0 | Page 32 of 36

Description

0x0 selects Channel 0 comparator high.

0x1 selects Channel 0 comparator low.

0x2 selects Channel 1 comparator high.

0x3 selects Channel 1 comparator low.

0x4 selects Channel 2 comparator high.

0x5 selects Channel 2 comparator low.

0x6 selects Channel 3 comparator high.

0x7 selects Channel 3 comparator low.

TMU Arm Enable. A zero tristates the TMU Stop output.

TMU Arm Channel Select Multiplexer. A binary encoded data field.

0x0 selects Channel 0 comparator high.

0x1 selects Channel 0 comparator low.

0x2 selects Channel 1 comparator high.

0x3 selects Channel 1 comparator low.

0x4 selects Channel 2 comparator high.

0x5 selects Channel 2 comparator low.

0x6 selects Channel 3 comparator high.

0x7 selects Channel 3 comparator low.

Reset State

0

0x00

Name:

Address:

Type:

Channel Multiplex Enable

0x1D

Read/Write

Table 37. Channel Multiplex Enable

Position

Description

Bits[15:02]

Not Used.

Bit 01

CH2 Multiplex Enable. This channel can be 2-way multiplexed. Setting this bit to 1 enables Channel 3

to be multiplexed on Channel 2.

Bit 00

CH0 Multiplex Enable. This channel can be 2-way multiplexed. Setting this bit to 1 enables Channel 1

to be multiplexed on Channel 0.

Reset State

0x0000

0

0

Name:

Address:

Type:

Channel Status

0x1E

Read

Table 38. Channel Status

Position

Bit 15

Description

Channel 3 Failure. This indicates that the channel had a failure. This signal is the Logic OR of the

accumulated fail registers (AFRs) of the channel. More details of the fail can be found by reading the

AFRs or fail counter for Channel 3.

Channel 2 Failure. This indicates that the channel had a failure. This signal is the Logic OR of the

accumulated fail registers (AFRs) of the channel. More details of the fail can be found by reading the

AFRs or fail counter for Channel 2.

Channel 1 Failure. This indicates that the channel had a failure. This signal is the Logic OR of the

accumulated fail registers (AFRs) of the channel. More details of the fail can be found by reading the

AFRs or fail counter for Channel 1.

Channel 0 Failure. This indicates that the channel had a failure. This signal is the Logic OR of the

accumulated fail registers (AFRs) of the channel. More details of the fail can be found by reading the

AFRs or fail counter for Channel 0.

Channel 3 Timing Error. This indicates that the channel had a timing error. This signal is the Logic OR of

the timing error flags of the channel. More details of the error can be found by reading the error flags

for Channel 3.

Reset State

0x0

Bit 14

0x0

Bit 13

0x0

Bit 12

0x0

Bit 11

0x0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADAU1401 | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1401YSTZ | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1401YSTZ-RL | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1513 | Class-D Audio Power Stage |

| ADAU1513ACPZ | Class-D Audio Power Stage |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADATE209 | 制造商:AD 制造商全稱(chēng):Analog Devices 功能描述:4.0 Gbps Dual Driver |

| ADATE209BBCZ | 制造商:Analog Devices 功能描述:4.0 GBPS DUAL DRIVER - Rail/Tube |

| ADATE209BCPZ | 制造商:Analog Devices 功能描述: |

| ADATE302-02 | 制造商:AD 制造商全稱(chēng):Analog Devices 功能描述:500 MHz Dual Integrated DCL with Differential Drive/Receive, Level Setting DACs, and Per Pin PMU |

| ADATE302-02BBCZ | 功能描述:IC DCL ATE 500MHZ DUAL 84CSPBGA RoHS:是 類(lèi)別:集成電路 (IC) >> 專(zhuān)用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類(lèi)型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類(lèi)型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。