- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374032 > ADSP-21061LKB-160 (ANALOG DEVICES INC) ADSP-2106x SHARC DSP Microcomputer Family PDF資料下載

參數(shù)資料

| 型號(hào): | ADSP-21061LKB-160 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | ADSP-2106x SHARC DSP Microcomputer Family |

| 中文描述: | 48-BIT, 40 MHz, OTHER DSP, PBGA225 |

| 封裝: | PLASTIC, BGA-225 |

| 文件頁(yè)數(shù): | 25/47頁(yè) |

| 文件大小: | 367K |

| 代理商: | ADSP-21061LKB-160 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

ADSP-21061/ADSP-21061L

–25–

REV. B

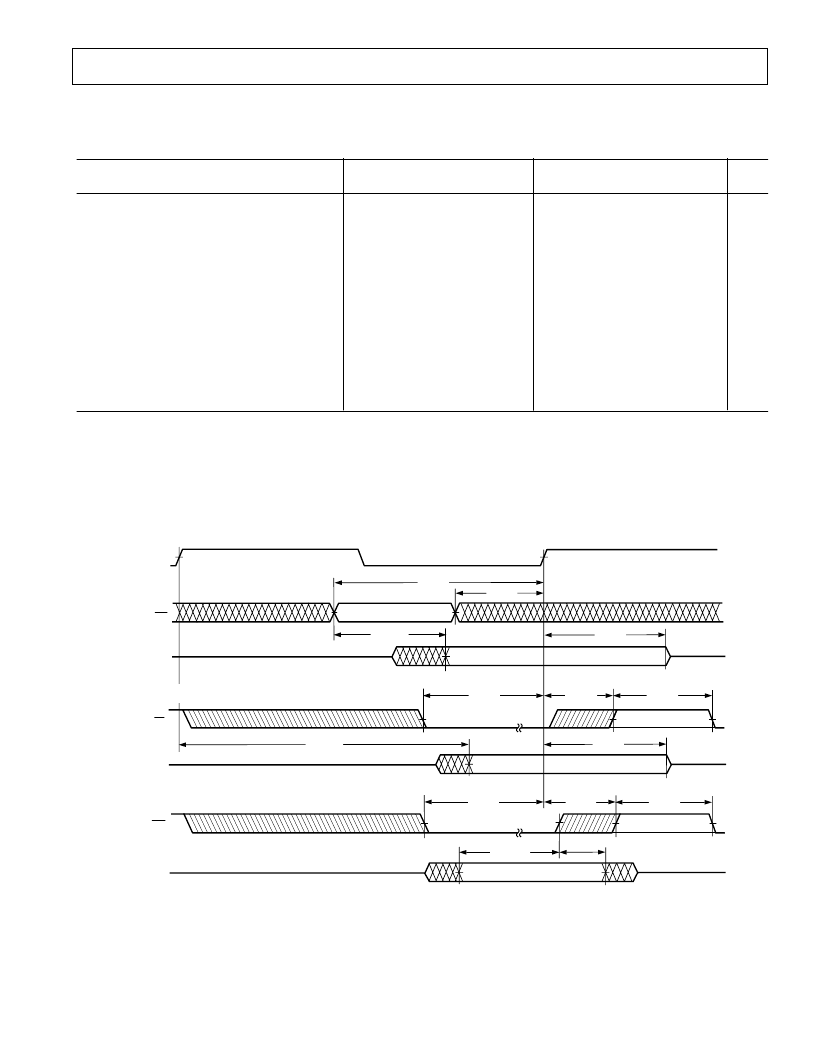

Synchronous Read/Write—Bus Slave

Use these specifications for ADSP-21061 bus master accesses of

a slave’s IOP registers or internal memory (in multiprocessor

memory space). The bus master must meet these (bus slave)

timing requirements.

ADSP-21061 (5 V)

Min

ADSP-21061L (3.3 V)

Min

Parameter

Max

Max

Unit

Timing Requirements:

t

SADRI

t

HADRI

t

SRWLI

t

HRWLI

t

HRWLI

Address,

SW

Setup before CLKIN

Address,

SW

Hold before CLKIN

RD

/

WR

Low Setup before CLKIN

1

RD

/

WR

Low Hold after CLKIN

RD

/

WR

Low Hold after CLKIN

44 MHz/50 MHz

2

RD

/

WR

Pulse High

Data Setup before

WR

High

Data Hold after

WR

High

14 + DT/2

14 + DT/2

ns

ns

ns

ns

5 + DT/2

5 + DT/2

8.5 + 5DT/16

–4 – 5DT/16

8.5 + 5DT/16

–4 – 5DT/16

8 + 7DT/16

8 + 7DT/16

–3.5 – 5DT/16

3

3

1

8 + 7DT/16

–3.5 – 5DT/16

3

3

1

8 + 7DT/16

ns

ns

ns

ns

t

RWHPI

t

SDATWH

t

HDATWH

Switching Characteristics:

t

SDDATO

t

DATTR

t

DACKAD

t

ACKTR

Data Delay after CLKIN

Data Disable after CLKIN

3

ACK Delay after Address,

SW

4

ACK Disable after CLKIN

4

19 + 5DT/16

7 – DT/8

8

6 – DT/8

19 + 5DT/16

7 – DT/8

8

6 – DT/8

ns

ns

ns

ns

0 – DT/8

0 – DT/8

–1 – DT/8

–1 – DT/8

NOTES

1

t

(min) = 9.5 + 5DT/16 when Multiprocessor Memory Space Wait State (MMSWS bit in WAIT register) is disabled; when MMSWS is enabled, t

SRWLI

(min)

= 4 + DT/8.

2

This specification applies to the ADSP-21061LKS-176 (3.3 V, 44 MHz) and the ADSP-21061KS-200 (5 V, 50 MHz), operating at t

CK

<25 ns. For all other devices,

use the preceding timing specification of the same name.

3

See

System Hold Time Calculation

under Test Conditions for calculation of hold times given capacitive and dc loads.

4

t

is true only if the address and

SW

inputs have setup times (before CLKIN) greater than 10 + DT/8 and less than 19 + 3DT/4. If the address and

SW

inputs have

setup times greater than 19 + 3DT/4, then ACK is valid 15.5 + DT/4 (max) after CLKIN. A slave that sees an address with an M field match will respond with ACK

regardless of the state of MMSWS or strobes. A slave will three-state ACK every cycle with t

ACKTR

.

CLKIN

ADDRESS

SW

ACK

RD

DATA

(OUT)

WR

WRITE ACCESS

t

SADRI

t

HADRI

t

DACKAD

t

ACKTR

t

RWHPI

t

HRWLI

t

SRWLI

t

SDDATO

t

DATTR

t

SRWLI

t

HRWLI

t

RWHPI

t

HDATWH

t

SDATWH

DATA

(IN)

READ ACCESS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-21061LKB-176 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21061LKS-160 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21061LKS-176 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21062CS-160 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21062KS-133 | ADSP-2106x SHARC DSP Microcomputer Family |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-21061LKB-176 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer Family |

| ADSP-21061LKBZ-160 | 功能描述:IC DSP CONTROLLER 32BIT 225-BGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號(hào)處理器) 系列:SHARC® 標(biāo)準(zhǔn)包裝:2 系列:StarCore 類型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時(shí)鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP21061LKS160 | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 40MHz 40MIPS 240-Pin MQFP Tray |

| ADSP-21061LKS-160 | 制造商:Rochester Electronics LLC 功能描述:ADSP-21061 1MBIT,40MHZ, 3V SHARC - Bulk 制造商:Analog Devices 功能描述:IC SHARC DSP 40MHZ 21061 MQFP240 |

| ADSP-21061LKS-176 | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 44MHz 44MIPS 240-Pin MQFP Tray 制造商:Rochester Electronics LLC 功能描述:ADSP-21061L 44HZ, 3V SHARC - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。