- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374033 > ADSP-21160N (Analog Devices, Inc.) Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection PDF資料下載

參數(shù)資料

| 型號: | ADSP-21160N |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 基準(zhǔn)電壓源/電流源 |

| 英文描述: | Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection |

| 中文描述: | 無電容,NMOS管,150mA的低壓差穩(wěn)壓器的反向電流保護(hù) |

| 文件頁數(shù): | 37/53頁 |

| 文件大小: | 1680K |

| 代理商: | ADSP-21160N |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

PRELIMINARY TECHNICAL DATA

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog

Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing.

37

REV. PrB

For current information contact Analog Devices at 800/262-5643

ADSP-21160N

April 2002

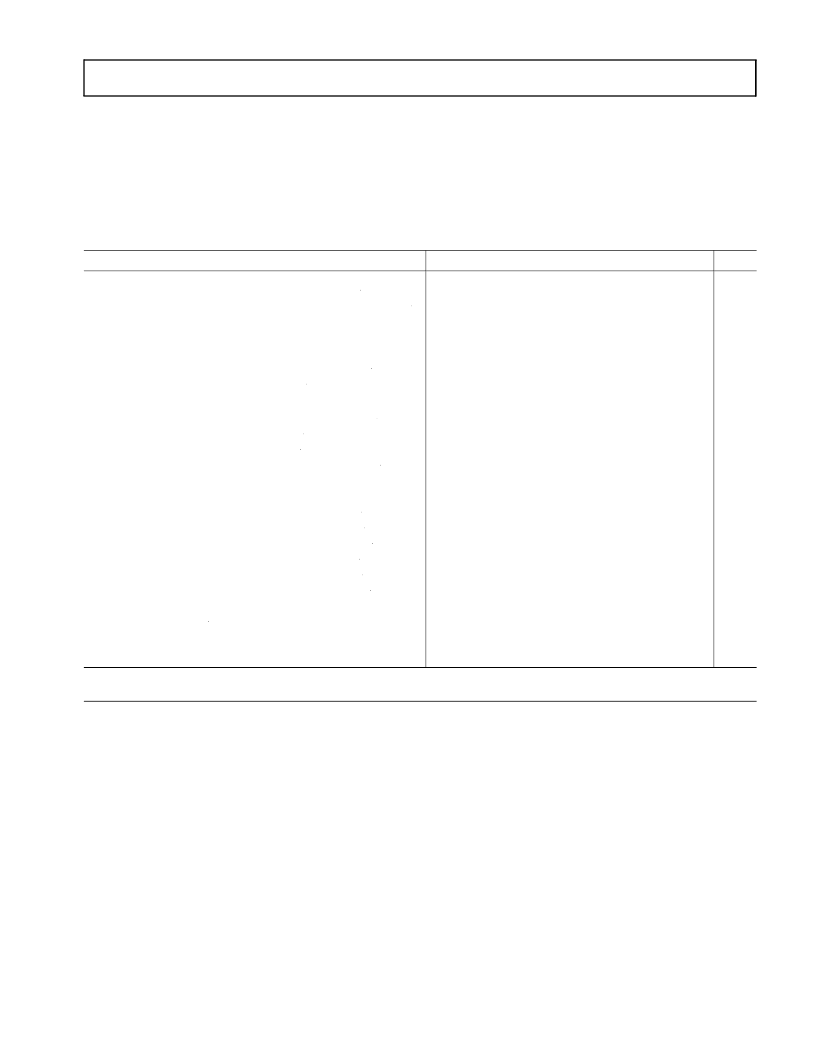

DMA Handshake

These specifications describe the three DMA handshake modes. In all three modes

DMAR

is used to initiate transfers. For

handshake mode,

DMAG

controls the latching or enabling of data externally. For external handshake mode, the data transfer

is controlled by the ADDR31–0,

RDx

,

WRx

, PAGE,

MS3–0

, ACK, and

DMAG

signals. For Paced Master mode, the data

transfer is controlled by ADDR31–0,

RDx

,

WRx

,

MS3–0

, and ACK (not

DMAG

). For Paced Master mode, the Memory

Read-Bus Master, Memory Write-Bus Master, and Synchronous Read/Write-Bus Master timing specifications for

ADDR31–0,

RDx

,

WRx

,

MS3–0

, PAGE, DATA63–0, and ACK also apply.

Table 18. DMA Handshake

Parameter

Timing Requirements:

t

SDRC

t

WDR

t

SDATDGL

t

HDATIDG

t

DATDRH

t

DMARLL

t

DMARH

Switching Characteristics:

t

DDGL

t

WDGH

t

WDGL

t

HDGC

t

VDATDGH

t

DATRDGH

t

DGWRL

t

DGWRH

t

DGWRR

t

DGRDL

t

DRDGH

t

DGRDR

t

DGWR

Min

Max

Unit

DMARx

Setup Before CLKIN

1

DMARx

Width Low (Nonsynchronous)

2

Data Setup After

DMAGx

Low

3

Data Hold After

DMAGx

High

Data Valid After

DMARx

High

3

DMARx

Low Edge to Low Edge

4

DMARx

Width High

2

1

Only required for recognition in the current cycle.

2

Maximum throughput using

DMARx/DMAGx

handshaking equals t

WDR

+ t

DMARH

= (0.5t

CCLK

+1) + (0.5t

CCLK

+1)=12.5 ns (80 MHz). This throughput

limit applies to non-synchronous access mode only.

3

t

SDATDGL

is the data setup requirement if

DMARx

is not being used to hold off completion of a write. Otherwise, if

DMARx

low holds off completion of

the write, the data can be driven t

DATDRH

after

DMARx

is brought high.

4

Use t

DMARLL

if

DMARx

transitions synchronous with CLKIN. Otherwise, use t

WDR

and t

DMARH

.

5

t

VDATDGH

is valid if

DMARx

is not being used to hold off completion of a read. If

DMARx

is used to prolong the read, then

t

VDATDGH

= t

CK

– .25t

CCLK

– 8 + (n × t

CK

) where n equals the number of extra cycles that the access is prolonged.

6

See

Example System Hold Time Calculation on page 47

for calculation of hold times given capacitive and dc loads.

7

This parameter applies for synchronous access mode only.

3

0.5t

CCLK

+1

ns

ns

ns

ns

ns

ns

ns

t

CK

–0.5t

CCLK

–7

2

t

CK

+3

t

CK

0.5t

CCLK

+1

DMAGx

Low Delay After CLKIN

DMAGx

High Width

DMAGx

Low Width

DMAGx

High Delay After CLKIN

Data Valid Before

DMAGx

High

5

Data Disable After

DMAGx

High

6

WRx

Low Before

DMAGx

Low

DMAG

x Low Before

WRx

High

WRx

High Before

DMAGx

High

7

RDx

Low Before

DMAGx

Low

RDx

Low Before

DMAGx

High

RDx

High Before

DMAGx

High

7

DMAGx

High to

WRx

,

RDx

,

DMAGx

Low

Address/Select Valid to

DMAGx

High

Address/Select Hold after

DMAGx

High

W = (number of wait states specified in WAIT register) t

CK

.

HI = t

CK

(if data bus idle cycle occurs, as specified in WAIT register; otherwise HI = 0).

0.25t

CCLK

+1

0.5t

CCLK

–1+HI

t

CK

–0.5t

CCLK

–1

t

CK

–0.25t

CCLK

+1.5

t

CK

–0.25t

CCLK

–8

0.25t

CCLK

–3

–1.5

t

CK

–0.5t

CCLK

–2+W

–1.5

–1.5

t

CK

–0.5t

CCLK

–2+W

–1.5

0.5t

CCLK

–2+HI

0.25t

CCLK

+9

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

t

CK

–0.25t

CCLK

+9

t

CK

–0.25t

CCLK

+5

0.25t

CCLK

+1.5

2

2

2

2

t

DADGH

t

DDGHA

18

1

ns

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-21160NCB-TBD | Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection |

| ADSP-21161N | DSP Microcomputer |

| ADSP-21161NCCA-100 | DSP Microcomputer |

| ADSP-21161NKCA-100 | DSP Microcomputer |

| ADSP-21262SBBC-150 | Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-21160NCB-100 | 功能描述:IC DSP CONTROLLER 32BIT 400BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號處理器) 系列:SHARC® 標(biāo)準(zhǔn)包裝:2 系列:StarCore 類型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21160NCB-TBD | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-21160NCBZ-100 | 功能描述:IC DSP CONTROLLER 32BIT 400-PBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號處理器) 系列:SHARC® 標(biāo)準(zhǔn)包裝:40 系列:TMS320DM64x, DaVinci™ 類型:定點(diǎn) 接口:I²C,McASP,McBSP 時鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:160kB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:0°C ~ 90°C 安裝類型:表面貼裝 封裝/外殼:548-BBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:548-FCBGA(27x27) 包裝:托盤 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21160NCE-100 | 制造商:Analog Devices 功能描述: |

| ADSP-21160NKB-100 | 功能描述:IC DSP CONTROLLER 32BIT 400BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號處理器) 系列:SHARC® 標(biāo)準(zhǔn)包裝:2 系列:StarCore 類型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:431-FCPBGA(20x20) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。