- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄374033 > ADSP-21266 (Analog Devices, Inc.) SHARC Embedded Processor PDF資料下載

參數(shù)資料

| 型號(hào): | ADSP-21266 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | SHARC Embedded Processor |

| 中文描述: | SHARC處理器嵌入式處理器 |

| 文件頁(yè)數(shù): | 6/44頁(yè) |

| 文件大小: | 426K |

| 代理商: | ADSP-21266 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

Rev. B

|

Page 6 of 44

|

May 2005

ADSP-21266

Fourier transforms. The two DAGs of the ADSP-21266 contain

sufficient registers to allow the creation of up to 32 circular buff-

ers (16 primary register sets, 16 secondary). The DAGs

automatically handle address pointer wraparound, reduce over-

head, increase performance, and simplify implementation.

Circular buffers can start and end at any memory location.

Flexible Instruction Set

The 48-bit instruction word accommodates a variety of parallel

operations for concise programming. For example, the

ADSP-21266 can conditionally execute a multiply, an add, and a

subtract in both processing elements while branching and fetch-

ing up to four 32-bit values from memory—all in a single

instruction.

ADSP-21266 MEMORY AND I/O INTERFACE

FEATURES

The ADSP-21266 adds the following architectural features to

the SIMD SHARC family core:

Dual-Ported On-Chip Memory

The ADSP-21266 contains two megabits of internal SRAM and

four megabits of internal mask-programmable ROM. Each

block can be configured for different combinations of code and

data storage (see memory map,

Figure 3

). Each memory block is

dual-ported for single-cycle, independent accesses by the core

processor and I/O processor. The dual-ported memory, in com-

bination with three separate on-chip buses, allows two data

transfers from the core and one from the I/O processor, in a sin-

gle cycle.

The ADSP-21266 is available with a variety of multichannel

surround-sound decoders, preprogrammed in on-chip ROM

memory.

Table 2

indicates the configurations of decoder algo-

rithms provided.

The ADSP-21266’s SRAM can be configured as a maximum of

64K words of 32-bit data, 128K words of 16-bit data, 42K words

of 48-bit instructions (or 40-bit data), or combinations of differ-

ent word sizes up to two megabits. All of the memory can be

accessed as 16-bit, 32-bit, 48-bit, or 64-bit words. A 16-bit float-

ing-point storage format is supported that effectively doubles

the amount of data that may be stored on-chip. Conversion

between the 32-bit floating-point and 16-bit floating-point for-

mats is performed in a single instruction. While each memory

block can store combinations of code and data, accesses are

most efficient when one block stores data using the DM bus for

transfers, and the other block stores instructions and data using

the PM bus for transfers.

Using the DM bus and PM buses, with one dedicated to each

memory block, assures single-cycle execution with two data

transfers. In this case, the instruction must be available in

the cache.

DMA Controller

The ADSP-21266’s on-chip DMA controller allows zero-over-

head data transfers without processor intervention. The DMA

controller operates independently and invisibly to the processor

core, allowing DMA operations to occur while the core is simul-

taneously executing its program instructions. DMA transfers

can occur between the ADSP-21266’s internal memory and its

serial ports, the SPI-compatible (serial peripheral interface)

port, the IDP (input data port), parallel data acquisition port

(PDAP), or the parallel port. Twenty-two channels of DMA are

available on the ADSP-21266—one for the SPI interface, 12 via

the serial ports, eight via the input data port, and one via the

processor’s parallel port. Programs can be downloaded to the

ADSP-21266 using DMA transfers. Other DMA features

include interrupt generation upon completion of DMA trans-

fers, and DMA chaining for automatic linked DMA transfers.

Digital Audio Interface (DAI)

The digital audio interface provides the ability to connect vari-

ous peripherals to any of the SHARC’s DAI pins (DAI_P20

–

1).

Connections are made using the signal routing unit (SRU,

shown in the block diagram

on Page 1

).

The SRU is a matrix routing unit (or group of multiplexers) that

enables the peripherals provided by the DAI to be intercon-

nected under software control. This allows easy use of the DAI

associated peripherals for a much wider variety of applications

by using a larger set of algorithms than is possible with noncon-

figurable signal paths.

The DAI also includes six serial ports, two precision clock gen-

erators (PCGs), an input data port (IDP), six flag outputs and

six flag inputs, and three timers. The IDP provides an additional

input path to the ADSP-21266 core, configurable as either eight

channels of I

2

S or serial data, or as seven channels plus a single

20-bit wide synchronous parallel data acquisition port. Each

data channel has its own DMA channel that is independent

from the ADSP-21266’s serial ports.

For complete information on using the DAI, see the

ADSP-2126x SHARC DSP Peripherals Manual

.

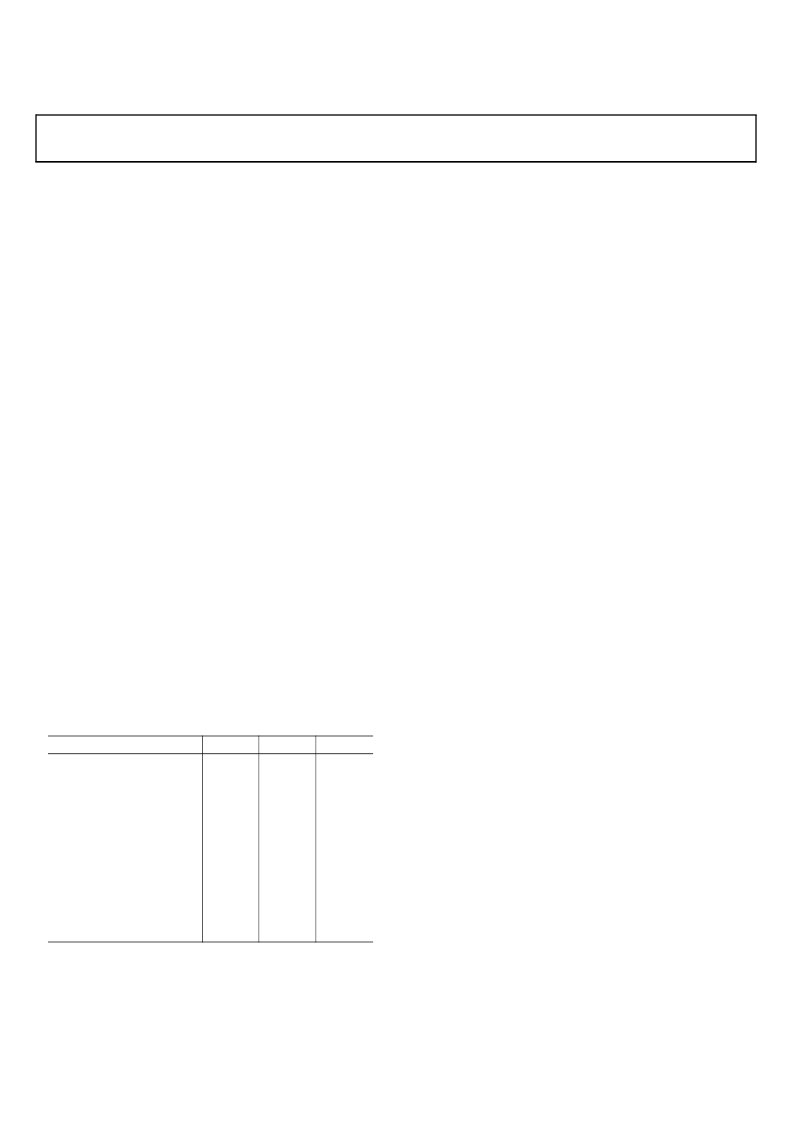

Table 2. Multichannel Surround-Sound Decoder Algorithms

in On-Chip ROM

Algorithms

PCM

AC-3

DTS 96/24

AAC (LC)

B ROM

Yes

Yes

v2.2

Yes

C ROM

Yes

Yes

v2.3

Yes

D ROM

Yes

Yes

v2.3

Coef-

ficients

only

Yes

No

Yes

Yes

Yes

WMAPRO 7.1 96 KHz

MPEG2 BC 2ch

Noise

DPL2x/EX

Neo:6/ES (v2.5046)

No

Yes

Yes

DPL2

Yes

No

Yes

Yes

Yes

Yes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-21266SKBC-2B | SHARC Embedded Processor |

| ADSP-21266SKBCZ-2B | SHARC Embedded Processor |

| ADSP-21266SKBCZ-2C | SHARC Embedded Processor |

| ADSP-21266SKBCZ-2D | SHARC Embedded Processor |

| ADSP-21266SKSTZ-1B | SHARC Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-21266_07 | 制造商:AD 制造商全稱(chēng):Analog Devices 功能描述:Embedded Processor |

| ADSP-21266KSTZ-1C | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-21266KSTZ-2C | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-21266SKBC-2B | 制造商:Analog Devices 功能描述:DSP FLOATING PT 32BIT 200MHZ 200MIPS 136CSPBGA - Trays |

| ADSP-21266SKBCZ-2B | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。