- 您現在的位置:買賣IC網 > PDF目錄374037 > ADSP-BF561SKBCZ600 (ANALOG DEVICES INC) Blackfin Embedded Symmetric Multi-Processor PDF資料下載

參數資料

| 型號: | ADSP-BF561SKBCZ600 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | Blackfin Embedded Symmetric Multi-Processor |

| 中文描述: | 32-BIT, 133 MHz, OTHER DSP, PBGA256 |

| 封裝: | 12 X 12 MM, LEAD FREE, MO-225, MBGA-256 |

| 文件頁數: | 22/52頁 |

| 文件大小: | 508K |

| 代理商: | ADSP-BF561SKBCZ600 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Rev. PrC

|

Page 22 of 52

|

April 2004

ADSP-BF561

Preliminary Technical Data

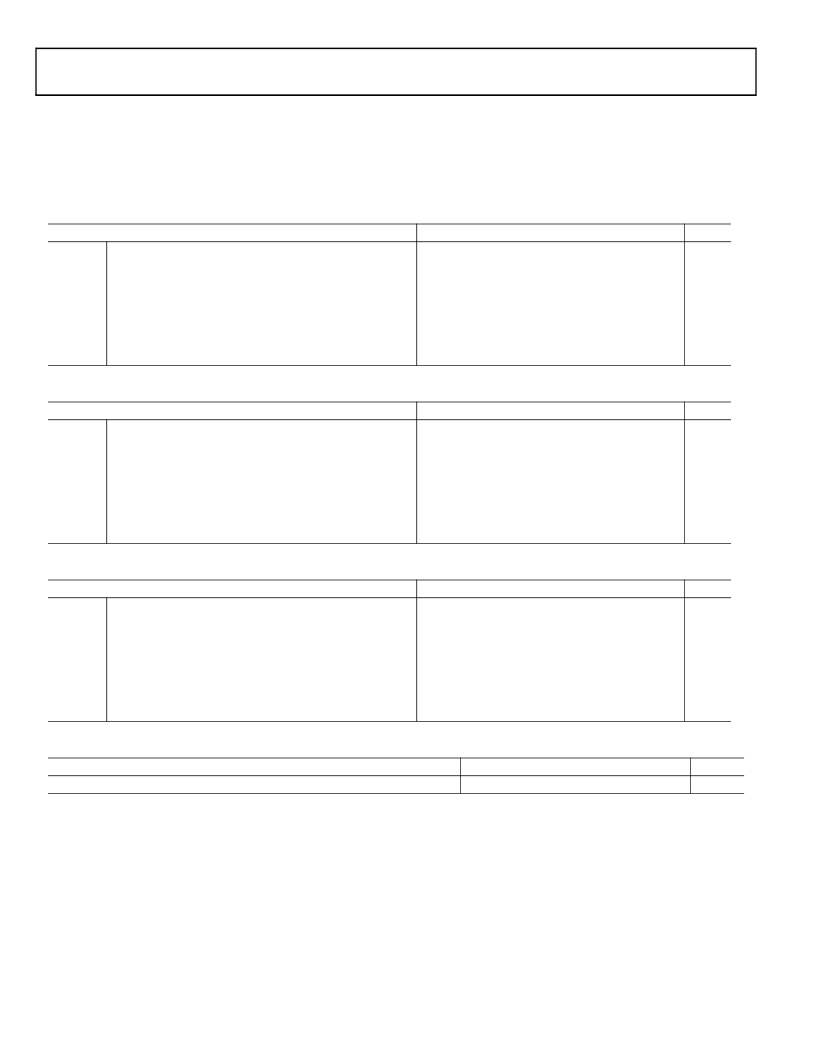

TIMING SPECIFICATIONS

Table 9

and

Table 12

describe the timing requirements for the

ADSP-BF561 clocks. Take care in selecting MSEL, SSEL, and

CSEL ratios so as not to exceed the maximum core clock, system

clock and Voltage Controlled Oscillator (VCO) operating fre-

quencies, as described in

Absolute Maximum Ratings on

Page 21

.

Table 12

describes Phase-Locked Loop operating

conditions.

Table 9. Core and System Clock Requirements—ADSP-BF561SKBCZ500

Parameter

t

CCLK

t

CCLK

t

CCLK

t

CCLK

t

CCLK

t

CCLK

t

CCLK

Minimum

na

na

2

2.25

2.70

3.20

4.00

Maximum

Unit

ns

ns

ns

ns

ns

ns

ns

Core Cycle Period (V

DDINT

=1.4 V–± 50 mV)

Core Cycle Period (V

DDINT

=1.35 V–5%)

Core Cycle Period (V

DDINT

=1.2 V–5%)

Core Cycle Period (V

DDINT

=1.1 V–5%)

Core Cycle Period (V

DDINT

=1.0 V–5%)

Core Cycle Period (V

DDINT

=0.9 V–5%)

Core Cycle Period (V

DDINT

=0.8 V)

Table 10. Core and System Clock Requirements—ADSP-BF561SKBCZ600X

Parameter

t

CCLK

t

CCLK

t

CCLK

t

CCLK

t

CCLK

t

CCLK

t

CCLK

Minimum

na

na

1.66

2.25

2.70

3.20

4.00

Maximum

Unit

ns

ns

ns

ns

ns

ns

ns

Core Cycle Period (V

DDINT

=1.4 V–± 50 mV)

Core Cycle Period (V

DDINT

=1.35 V–5%)

Core Cycle Period (V

DDINT

=1.2 V–5%)

Core Cycle Period (V

DDINT

=1.1 V–5%)

Core Cycle Period (V

DDINT

=1.0 V–5%)

Core Cycle Period (V

DDINT

=0.9 V–5%)

Core Cycle Period (V

DDINT

=0.8 V)

Table 11. Core and System Clock Requirements—ADSP-BF561SBB600

Parameter

t

CCLK

t

CCLK

t

CCLK

t

CCLK

t

CCLK

t

CCLK

t

CCLK

Minimum

na

1.66

2.0

2.25

2.70

3.20

4.00

Maximum

Unit

ns

ns

ns

ns

ns

ns

ns

Core Cycle Period (V

DDINT

=1.4 V–± 50 mV)

Core Cycle Period (V

DDINT

=1.35 V–5%)

Core Cycle Period (V

DDINT

=1.2 V–5%)

Core Cycle Period (V

DDINT

=1.1 V–5%)

Core Cycle Period (V

DDINT

=1.0 V–5%)

Core Cycle Period (V

DDINT

=0.9 V–5%)

Core Cycle Period (V

DDINT

=0.8 V)

Table 12. Phase-Locked Loop Operating Conditions

Parameter

Voltage Controlled Oscillator (VCO) Frequency

Minimum

50

Maximum

Maximum CCLK

Unit

MHz

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-BF561SKBCZ500 | Blackfin Embedded Symmetric Multi-Processor |

| ADSP-BF561 | Synchronous 4-Bit Up/Down Binary Counters With Dual Clock and Clear 16-PDIP 0 to 70 |

| ADSP-BF561SBB500 | Blackfin Embedded Symmetric Multi-Processor |

| ADSP21020 | 32/40-Bit IEEE Floating-Point DSP Microprocessor |

| ADSP-21020BG-100 | 32/40-Bit IEEE Floating-Point DSP Microprocessor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-BF561SKBCZ-6A | 功能描述:IC DSP CTRLR 32B 600MHZ 256CPBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:Blackfin® 標準包裝:40 系列:TMS320DM64x, DaVinci™ 類型:定點 接口:I²C,McASP,McBSP 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:160kB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:0°C ~ 90°C 安裝類型:表面貼裝 封裝/外殼:548-BBGA,FCBGA 供應商設備封裝:548-FCBGA(27x27) 包裝:托盤 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-BF561SKBCZ-6A | 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

| ADSP-BF561SKBCZ-6V | 功能描述:IC DSP 32BIT 600MHZ 256CSPBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:Blackfin® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-BF561SKBCZC70 | 制造商:Analog Devices 功能描述: |

| ADSPBF561SKBCZ-C70 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發布緊急采購,3分鐘左右您將得到回復。