- 您現在的位置:買賣IC網 > PDF目錄374044 > ADV601LC (Analog Devices, Inc.) Ultralow Cost Video Codec PDF資料下載

參數資料

| 型號: | ADV601LC |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 視頻Codec |

| 英文描述: | Ultralow Cost Video Codec |

| 中文描述: | 超低成本視頻編解碼器 |

| 文件頁數: | 3/52頁 |

| 文件大小: | 606K |

| 代理商: | ADV601LC |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADV601

–3–

REV. 0

application. The sub-band coding architecture of the ADV601

provides a number of options to stretch compression perfor-

mance. These options are outlined on in the Applying the

ADV601 section.

The DSP serial port interface (SPORT) enables performance of

Bin Width calculations on a DSP instead of the host. The ADV601

transfers current video field statistics to the DSP and receives Bin

Width data from the DSP as packet I/O through the DSP Inter-

face. A generic fixed-point DSP (i.e., the ADSP-2105 low cost,

fixed-point DSP) is more than adequate for these calculations.

INTERNAL ARCHITECTURE

The ADV601 is composed of nine blocks. Four of these blocks

are interface blocks and five are processing blocks. The interface

blocks are the Digital Video I/O Port, the Host I/O Port, exter-

nal DRAM manager, and the DSP serial I/O Port. The process-

ing blocks are the Wavelet Kernel, the On-Chip Transform

Buffer, the Programmable Quantizer, the Run Length Coder,

and the Huffman Coder.

Digital Video I/O Port

Provides a real-time uncompressed video interface to support a

broad range of component digital video formats, including “D1.”

Host I/O Port and FIFO

Carries control, status, and compressed video to and from the

host processor. A 512 position by 32-bit FIFO buffers the com-

pressed video stream between the host and the Huffman Coder.

DRAM Manager

Performs all tasks related to writing, reading, and refreshing the

external DRAM. The external host buffer DRAM is used for

reordering and buffering quantizer input and output values.

Serial Port (to Optional DSP)

Supports, during encode only, communication of wavelet statis-

tics between the Wavelet Kernel and the DSP and quantizer

control information between the DSP and the Quantizer block.

The user programmed compression ratio is also sent from the

ADV601 host interface to the DSP automatically. Note that a

host processor can be used to replace the DSP functionality in

computer applications.

Wavelet Kernel (Filters, Decimator, and Interpolator)

Gathers statistics on a per field basis and includes a block of

filters, interpolators, and decimators. The kernel calculates

forward and backward bi-orthogonal, two-dimensional, sepa-

rable wavelet transforms on horizontal scanned video data. This

block uses the internal transform buffer when performing wave-

let transforms calculated on an entire image’s data and so

eliminates any need for extremely fast external memories in

an ADV601-based design.

On-Chip Transform Buffer

Provides an internal set of SRAM for use by the wavelet trans-

form kernel. Its function is to provide enough delay line storage

to support calculation of separable two dimensional wavelet

transforms for horizontally scanned images.

Programmable Quantizer

Quantizes wavelet coefficients. Quantize controls are calculated

by the external DSP or host processor during encode operations

and de-quantize controls are extracted from the compressed bit

stream during decode. Each quantizer Bin Width is computed

by the BW calculator software to maintain a constant com-

pressed bit rate or constant quality bit rate. A Bin Width is a per

block parameter the quantizer uses when determining the num-

ber of bits to allocate to each block (sub-band).

Run Length Coder

Performs run length coding on zero data and models nonzero

data, encoding or decoding for more efficient Huffman coding.

This data coding is optimized across the sub-bands and varies

depending on the block being coded.

Huffman Coder

Performs Huffman coder and decoder functions on quantized

run-length coded coefficient values. The Huffman coder/de-

coder uses three ROM-coded Huffman tables that provide ex-

cellent performance for wavelet transformed video.

GENERAL THEORY OF OPERATION

The ADV601 processor’s compression algorithm is based on the

bi-orthogonal (7, 9) wavelet transform, and implements field

independent sub-band coding. Sub-band coders transform two-

dimensional spatial video data into spatial frequency filtered

sub-bands. The quantization and entropy encoding processes

provide the ADV601’s data compression.

The wavelet theory, on which the ADV601 is based, is a new

mathematical apparatus first explicitly introduced by Morlet and

Grossman in their works on geophysics during the mid 80s.

This theory became very popular in theoretical physics and

applied math. The late 80s and 90s have seen a dramatic growth

in wavelet applications such as signal and image processing. For

more on wavelet theory by Morlet and Grossman, see

Decompo-

sition of Hardy Functions into Square Integrable Wavelets of Con-

stant Shape

(journal citation listed in References section).

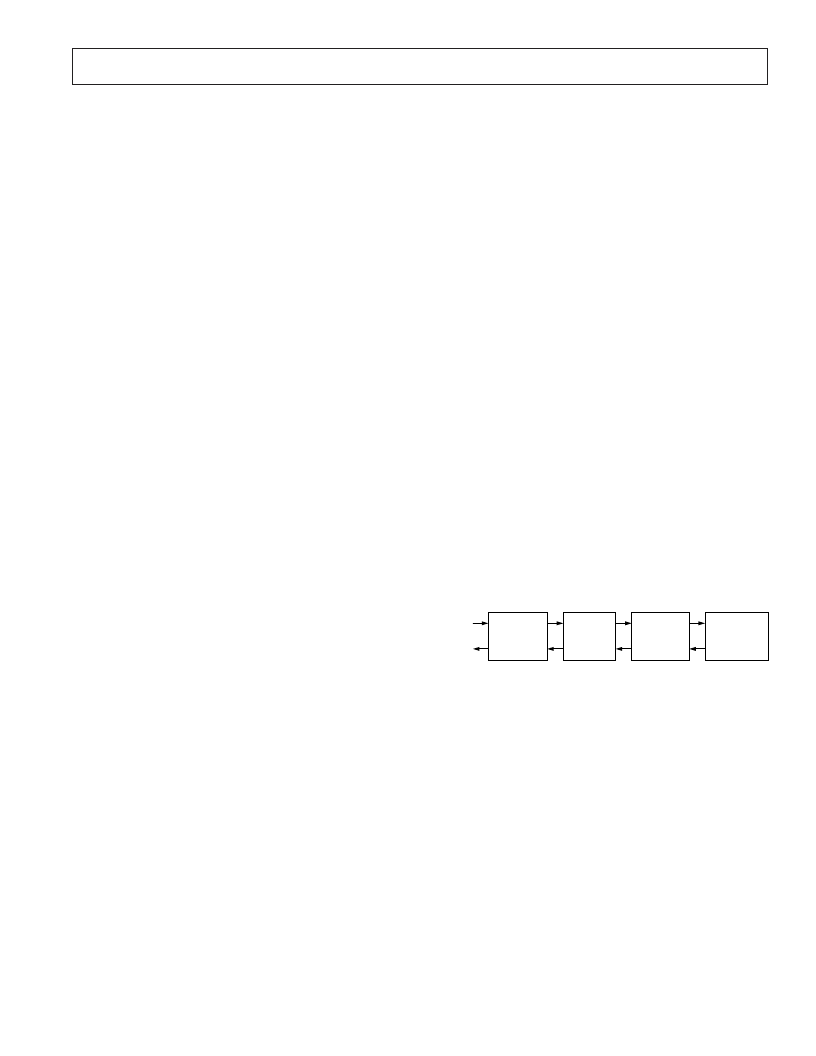

ENCODE

PATH

DECODE

PATH

WAVELET

KERNEL

FILTER BANK

ADAPTIVE

QUANTIZER

RUN LENGTH

CODER &

HUFFMAN

CODER

COMPRESSED

DATA

Figure 2. Encode and Decode Paths

References

For more information on the terms, techniques and underlying

principles referred to in this data sheet, you may find the follow-

ing reference texts useful. A reference text for general digital

video principles is:

Jack, K.,

Video Demystified:

A Handbook for the Digital Engineer

(High Text Publications, 1993) ISBN 1-878707-09-4

Three reference texts for wavelet transform background infor-

mation are:

Vetterli, M., Kovacevic, J.,

Wavelets And Sub-band Coding

(Prentice Hall, 1995) ISBN 0-13-097080-8

Benedetto, J., Frazier, M.,

Wavelets: Mathematics And Applica-

tions

(CRC Press, 1994) ISBN 0-8493-8271-8

Grossman, A., Morlet, J.,

Decomposition of Hardy Functions into

Square Integrable Wavelets of Constant Shape

, Siam. J. Math.

Anal., Vol. 15, No. 4, pp 723-736, 1984

相關PDF資料 |

PDF描述 |

|---|---|

| ADV601LCJST | Ultralow Cost Video Codec |

| ADV7120KP30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KP50 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KP80 | CMOS 80 MHz, Triple 8-Bit Video DAC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV601LCERAG1266B-0.5 | 制造商:Analog Devices 功能描述: |

| ADV601LCJST | 制造商:Analog Devices 功能描述:Ultralow Cost Video Codec 120-Pin LQFP 制造商:Analog Devices 功能描述:IC VIDEO CODEC |

| ADV601LCJSTRL | 制造商:Analog Devices 功能描述:Ultralow Cost Video Codec 120-Pin LQFP T/R |

| ADV601LCJSTZ | 功能描述:IC CODEC VIDEO DSP/SRL 120LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

| ADV601LCJSTZRL | 功能描述:IC CODEC VIDEO DSP/SRL 120LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。