- 您現在的位置:買賣IC網 > PDF目錄374044 > ADV601LC (Analog Devices, Inc.) Ultralow Cost Video Codec PDF資料下載

參數資料

| 型號: | ADV601LC |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 視頻Codec |

| 英文描述: | Ultralow Cost Video Codec |

| 中文描述: | 超低成本視頻編解碼器 |

| 文件頁數: | 49/52頁 |

| 文件大小: | 606K |

| 代理商: | ADV601LC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當前第49頁第50頁第51頁第52頁

ADV601

–49–

REV. 0

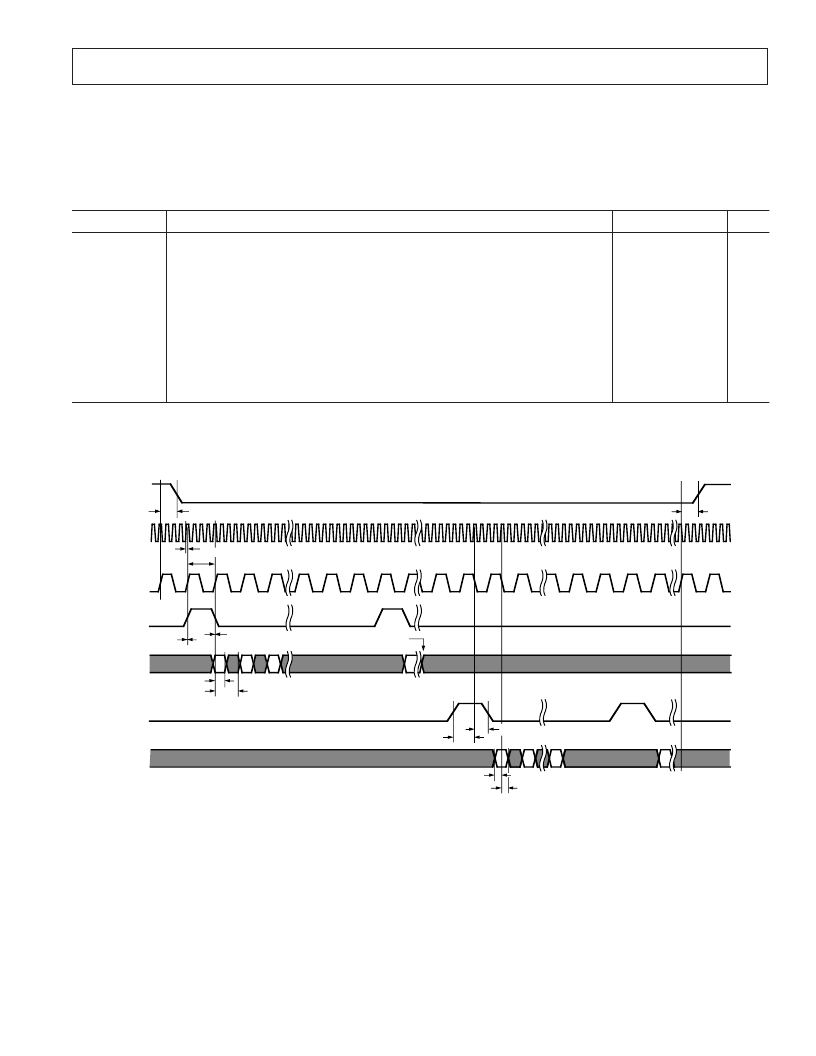

DSP Interface Timing

The diagram in this section shows transfer timing for one set of video statistics and calculated bin widths as they pass through the

ADV601’s DSP interface. Whenever an ADV601’s serial port is inactive, the codec’s TXD pin is three-stated and the codec ignores

the state of the RXD pin. Figure 41 illustrates the ADV601 serial interface’s signal, sample and frame relationships for the transmit

and receive modes.

Table XXXVII. DSP Read and Write Transfer Timing Parameters

Parameter

Description

Min

Max

Unit

t

TCLK_DIRQ_D

t

TCLK_DIRQ_OH

t

VCLK_TCLK_D

t

TCLK_TF_D

t

TCLK_TF_OH

t

TCLK_TXD_D

t

TCLK_TXD_OH

t

TCLK_RF_S

t

TCLK_RF_H

t

TCLK_RXD_S

t

TCLK_RXD_H

DIRQ

Signal, Transfer-Receive Cycle Start, Delay

DIRQ

Signal, Transfer-Receive Cycle End, Output Hold

TCLK

Signal, Referenced to VCLK, Delay

TF Signal, Transfer Frame Reference to TCLK, Delay

TF Signal, Transfer Frame Reference to TCLK, Output Hold

TXD Sample, Transfer Data, Delay (at 27 MHz VCLK)

TXD Sample, Transfer Data, Output Hold

RF Signal, Receive Frame Referenced to TCLK, Setup

RF Signal, Receive Frame Referenced to TCLK, Hold

RXD Sample, Receive Data, Setup

RXD Sample, Receive Data, Hold (at 27 MHz VCLK)

N/A

3

N/A

N/A

2

N/A

2

2

105

2

16.8

2

4

N/A

11

3

N/A

24.2

1

N/A

N/A

N/A

N/A

N/A

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

NOTES

1

Maximum t

TCLK_TXD_D

varies with VCLK according to the formula: t

TCLK_TXD_D

(MAX)

= 0.5 (VCLK Period) +4.7.

2

Minimum t

TCLK_RXD_H

varies with VCLK according to the formula: t

TCLK_RXD_H

(MIN)

= 1.5 (VCLK Period) –36.

(O)

DIRQ

DSP CALCULATES BIN WIDTHS

FROM VIDEO STATISTICS

(I) VCLK

(O) TCLK

TCLK PERIOD = 4

·

VCLK PERIOD

FIFTY-TWO 16-BIT WORDS TRANSFERRED BY THE ADV601

-- ADV601 REGISTERS 0x06 AND 0x80 THROUGH 0xB2

EIGHTY-FOUR 16-BIT WORDS TRANSFERRED BY THE DSP

-- ADV601 REGISTERS 0x100 THROUGH 0x153

(O) TF

(O) TXD

t

TCLK_TXD_OH

TCLK_TXD_D

t

TCLK_RF_S

t

TCLK_RXD_H

t

TCLK_RXD_S

(I) RF

(I) RXD

t

TCLK_DIRQ_OH

t

TCLK_DIRQ_D

t

TCLK_TF_D

t

VCLK_TCLK_D

t

TCLK_RF_H

t

TCLK_TF_OH

Figure 41. DSP Read and Write Transfer Timing

相關PDF資料 |

PDF描述 |

|---|---|

| ADV601LCJST | Ultralow Cost Video Codec |

| ADV7120KP30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KP50 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120KP80 | CMOS 80 MHz, Triple 8-Bit Video DAC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV601LCERAG1266B-0.5 | 制造商:Analog Devices 功能描述: |

| ADV601LCJST | 制造商:Analog Devices 功能描述:Ultralow Cost Video Codec 120-Pin LQFP 制造商:Analog Devices 功能描述:IC VIDEO CODEC |

| ADV601LCJSTRL | 制造商:Analog Devices 功能描述:Ultralow Cost Video Codec 120-Pin LQFP T/R |

| ADV601LCJSTZ | 功能描述:IC CODEC VIDEO DSP/SRL 120LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

| ADV601LCJSTZRL | 功能描述:IC CODEC VIDEO DSP/SRL 120LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:- 標準包裝:2,500 系列:- 類型:立體聲音頻 數據接口:串行 分辨率(位):18 b ADC / DAC 數量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。