- 您現在的位置:買賣IC網 > PDF目錄379696 > ATT3020-70M44I (Electronic Theatre Controls, Inc.) Field-Programmable Gate Arrays PDF資料下載

參數資料

| 型號: | ATT3020-70M44I |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | FPGA |

| 英文描述: | Field-Programmable Gate Arrays |

| 中文描述: | 現場可編程門陣列 |

| 文件頁數: | 17/80頁 |

| 文件大?。?/td> | 528K |

| 代理商: | ATT3020-70M44I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Lucent Technologies Inc.

17

Data Sheet

February 1997

ATT3000 Series Field-Programmable Gate Arrays

Configuration

Initialization Phase

An internal power-on-reset circuit is triggered when

power is applied. When V

CC

reaches the voltage where

portions of the FPGA begin to operate (2.5 V to 3 V),

the programmable I/O output buffers are disabled and a

high-impedance pull-up resistor is provided for the user

I/O pins. A time-out delay is initiated to allow the power

supply voltage to stabilize. During this time, the power-

down mode is inhibited. The initialization state time-out

(about 11 ms to 33 ms) is determined by a 14-bit

counter driven by a self-generated, internal timer. This

nominal 1 MHz timer is subject to variations with pro-

cess, temperature, and power supply over the range of

0.5 MHz to 1.5 MHz. As shown in Table 2, five configu-

ration mode choices are available, as determined by

the input levels of three mode pins: M0, M1, and M2.

In master configuration mode, the FPGA becomes the

source of configuration clock (CCLK). Beginning con-

figuration of devices using peripheral or slave modes

must be delayed long enough for their initialization to

be completed. An FPGA with mode lines selecting a

master configuration mode extends its initialization

state using four times the delay (43 ms to 130 ms) to

ensure that all daisy-chained slave devices it may be

driving will be ready, even if the master is very fast and

the slave(s), very slow (see Figure 18). At the end of

initialization, the FPGA enters the clear state where it

clears configuration memory. The active-low, open-

drain initialization signal

INIT

indicates when the initial-

ization and clear states are complete. The FPGA tests

for the absence of an external active-low

RESET

before

it makes a final sample of the mode lines and enters

the configuration state. An external wired-AND of one

or more

INIT

pins can be used to control configuration

by the assertion of the active-low

RESET

of a master

mode device or to signal a processor that the FPGAs

are not yet initialized.

If a configuration has begun, a reassertion of

RESET

for

a minimum of three internal timer cycles will be recog-

nized and the FPGA will initiate an abort, returning to

the clear state to clear the partially loaded configura-

tion memory words. The FPGA will then resample

RESET

and the mode lines before reentering the con-

figuration state.

A reprogram is initiated when a configured FPGA

senses a high-to-low transition on the DONE/

PROG

package pin. The FPGA returns to the clear state

where configuration memory is cleared and mode lines

resampled, as for an aborted configuration. The com-

plete configuration program is

cleared and loaded dur-

ing each configuration program cycle.

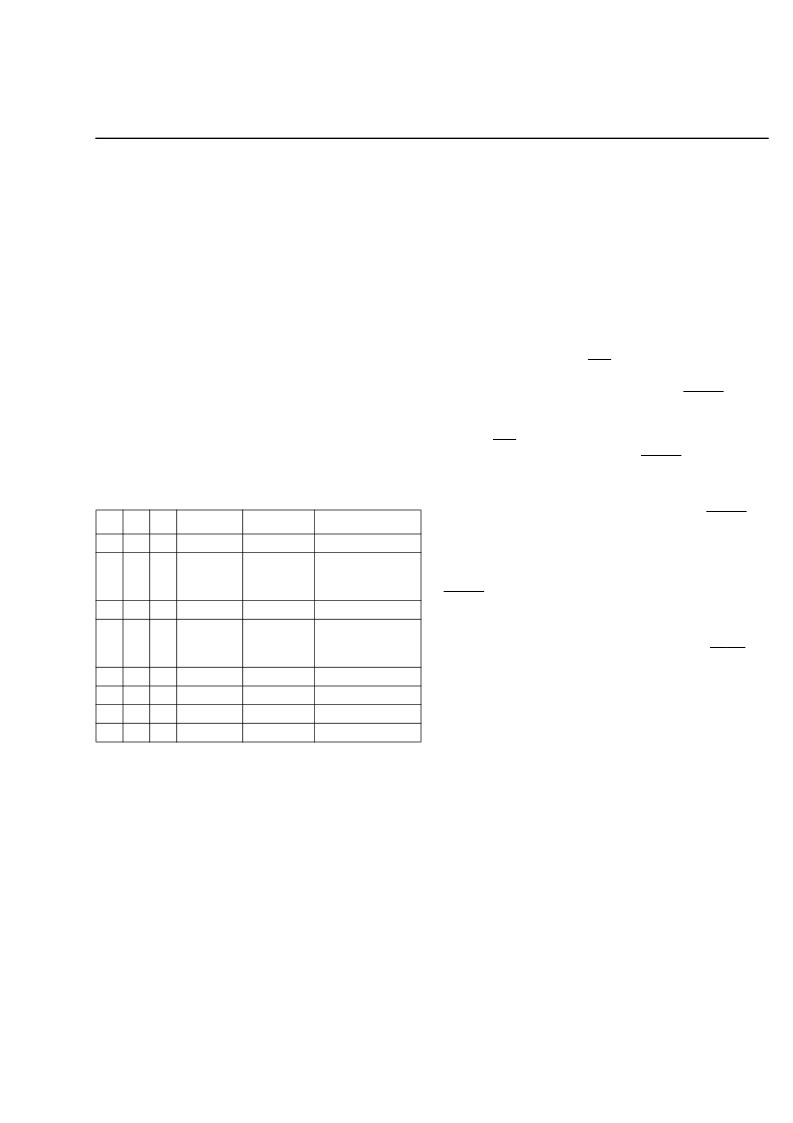

Table 2. Configuration Modes

M0 M1 M2

Clock

Mode

Data

0

0

0

0

0

1

Active

Active

Master

Master

Bit Serial

Byte Wide

(Address = 0000

up)

—

Byte Wide

(Address = FFFF

down)

—

Byte Wide

—

Bit Serial

0

0

1

1

0

1

—

Reserved

Master

Active

1

1

1

1

0

0

1

1

0

1

0

1

—

Reserved

Peripheral

Reserved

Slave

Active

—

Passive

相關PDF資料 |

PDF描述 |

|---|---|

| ATT3020-70M68I | Field-Programmable Gate Arrays |

| ATT3020-70M84I | Field-Programmable Gate Arrays |

| ATT3020-70S132I | Field-Programmable Gate Arrays |

| ATT3020-70S44I | Field-Programmable Gate Arrays |

| ATT3020-70S68I | Field-Programmable Gate Arrays |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ATT3020-70M68 | 制造商:ATandT 功能描述:FPGA, 64 CLBS, 2000 GATES, 84 MHz, PQCC68 |

| ATT3020-70M68I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| ATT3020-70M84 | 制造商:AT&T 功能描述: 制造商:ATandT 功能描述: |

| ATT3020-70M84I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| ATT3020-70N100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發布緊急采購,3分鐘左右您將得到回復。