- 您現在的位置:買賣IC網 > PDF目錄21999 > EPF10K100EFC256-3 (Altera)IC FLEX 10KE FPGA 100K 256-FBGA PDF資料下載

參數資料

| 型號: | EPF10K100EFC256-3 |

| 廠商: | Altera |

| 文件頁數: | 29/100頁 |

| 文件大小: | 0K |

| 描述: | IC FLEX 10KE FPGA 100K 256-FBGA |

| 產品培訓模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標準包裝: | 90 |

| 系列: | FLEX-10KE® |

| LAB/CLB數: | 624 |

| 邏輯元件/單元數: | 4992 |

| RAM 位總計: | 49152 |

| 輸入/輸出數: | 191 |

| 門數: | 257000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 256-BGA |

| 供應商設備封裝: | 256-FBGA(17x17) |

| 其它名稱: | 544-2192 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

34

Altera Corporation

FLEX 10KE Embedded Programmable Logic Devices Data Sheet

Signals on the peripheral control bus can also drive the four global signals,

generated signal can drive a global signal, providing the same low-skew,

low-delay characteristics as a signal driven by an input pin. An LE drives

the global signal by driving a row line that drives the peripheral bus,

which then drives the global signal. This feature is ideal for internally

generated clear or clock signals with high fan-out. However, internally

driven global signals offer no advantage over the general-purpose

interconnect for routing data signals. The dedicated input pin should be

driven to a known logic state (such as ground) and not be allowed to float.

The chip-wide output enable pin is an active-high pin (DEV_OE) that can

be used to tri-state all pins on the device. This option can be set in the

Altera software. On EPF10K50E and EPF10K200E devices, the built-in I/O

pin pull-up resistors (which are active during configuration) are active

when the chip-wide output enable pin is asserted. The registers in the IOE

can also be reset by the chip-wide reset pin.

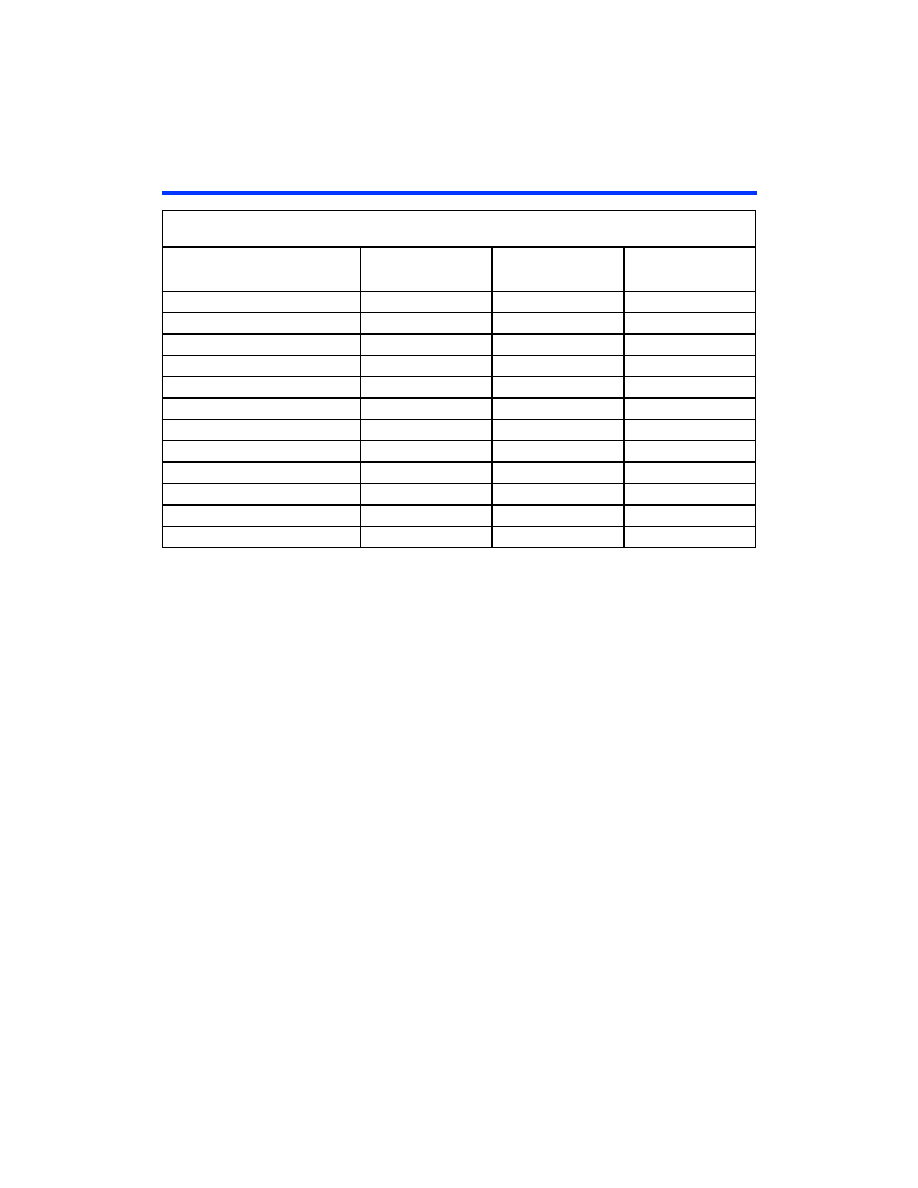

Table 9. Peripheral Bus Sources for EPF10K100E, EPF10K130E, EPF10K200E & EPF10K200S Devices

Peripheral

Control Signal

EPF10K100E

EPF10K130E

EPF10K200E

EPF10K200S

OE0

Row A

Row C

Row G

OE1

Row C

Row E

Row I

OE2

Row E

Row G

Row K

OE3

Row L

Row N

Row R

OE4

Row I

Row K

Row O

OE5

Row K

Row M

Row Q

CLKENA0/CLK0/GLOBAL0

Row F

Row H

Row L

CLKENA1/OE6/GLOBAL1

Row D

Row F

Row J

CLKENA2/CLR0

Row B

Row D

Row H

CLKENA3/OE7/GLOBAL2

Row H

Row J

Row N

CLKENA4/CLR1

Row J

Row L

Row P

CLKENA5/CLK1/GLOBAL3

Row G

Row I

Row M

相關PDF資料 |

PDF描述 |

|---|---|

| EBC12DCMN | CONN EDGECARD 24POS .100 WW |

| DS1821T | IC THERMOMETER/STAT PROG TO-220 |

| EBC12DCMH | CONN EDGECARD 24POS .100 WW |

| DS1620S-D1 | IC THERMOMETER/STAT DIG 8-SOIC |

| EBC12DCMD | CONN EDGECARD 24POS .100 WW |

相關代理商/技術參數 |

參數描述 |

|---|---|

| EPF10K100EFC256-3DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EPF10K100EFC256-3N | 功能描述:FPGA - 現場可編程門陣列 FPGA - Flex 10K 624 LABs 191 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF10K100EFC484-1 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Flex 10K 624 LABs 338 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF10K100EFC484-1DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EPF10K100EFC484-1N | 功能描述:FPGA - 現場可編程門陣列 FPGA - Flex 10K 624 LABs 338 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發布緊急采購,3分鐘左右您將得到回復。