- 您現在的位置:買賣IC網 > PDF目錄385342 > GS88218 (GSI TECHNOLOGY) 512K x 18, 256K x 36 9Mb SCD/DCD Sync Burst SRAMs PDF資料下載

參數資料

| 型號: | GS88218 |

| 廠商: | GSI TECHNOLOGY |

| 英文描述: | 512K x 18, 256K x 36 9Mb SCD/DCD Sync Burst SRAMs |

| 中文描述: | 為512k × 18,256K × 36 9Mb以上SCD的/雙氰胺同步突發靜態存儲器 |

| 文件頁數: | 28/37頁 |

| 文件大小: | 751K |

| 代理商: | GS88218 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

GS88218/36BB/D-333/300/250/200/150

Rev: 1.02 10/2004

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

28/37

2002, GSI Technology

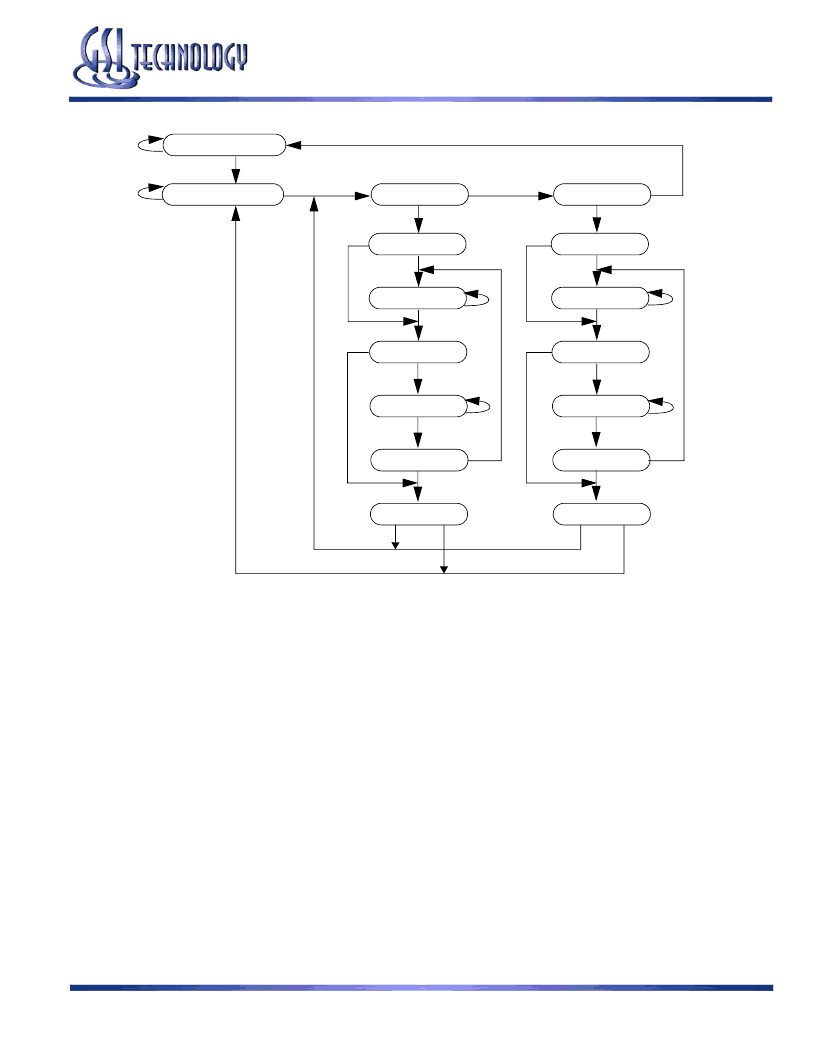

JTAG Tap Controller State Diagram

Instruction Descriptions

BYPASS

When the BYPASS instruction is loaded in the Instruction Register the Bypass Register is placed between TDI and TDO. This

occurs when the TAP controller is moved to the Shift-DR state. This allows the board level scan path to be shortened to facili-

tate testing of other devices in the scan path.

SAMPLE/PRELOAD

SAMPLE/PRELOAD is a Standard 1149.1 mandatory public instruction. When the SAMPLE / PRELOAD instruction is

loaded in the Instruction Register, moving the TAP controller into the Capture-DR state loads the data in the RAMs input and

I/O buffers into the Boundary Scan Register. Boundary Scan Register locations are not associated with an input or I/O pin, and

are loaded with the default state identified in the Boundary Scan Chain table at the end of this section of the datasheet. Because

the RAM clock is independent from the TAP Clock (TCK) it is possible for the TAP to attempt to capture the I/O ring contents

while the input buffers are in transition (i.e. in a metastable state). Although allowing the TAP to sample metastable inputs will

not harm the device, repeatable results cannot be expected. RAM input signals must be stabilized for long enough to meet the

TAPs input data capture set-up plus hold time (tTS plus tTH). The RAMs clock inputs need not be paused for any other TAP

operation except capturing the I/O ring contents into the Boundary Scan Register. Moving the controller to Shift-DR state then

places the boundary scan register between the TDI and TDO pins.

EXTEST

EXTEST is an IEEE 1149.1 mandatory public instruction. It is to be executed whenever the instruction register is loaded with

all logic 0s. The EXTEST command does not block or override the RAM’s input pins; therefore, the RAM’s internal state is

still determined by its input pins.

Select DR

Capture DR

0

Shift DR

Exit1 DR

Pause DR

Exit2 DR

Update DR

1

Select IR

Capture IR

0

Shift IR

Exit1 IR

Pause IR

Exit2 IR

Update IR

1

Test Logic Reset

Run Test Idle

0

1

0

1

1

0

1

1

1

0

0

1

1

0

0

0

0

1

1

0

0

0

0

0

1

1

1

1

相關PDF資料 |

PDF描述 |

|---|---|

| GS88218BB-150 | 512K x 18, 256K x 36 9Mb SCD/DCD Sync Burst SRAMs |

| GS88218BB-150I | 512K x 18, 256K x 36 9Mb SCD/DCD Sync Burst SRAMs |

| GS88236BD-150 | 512K x 18, 256K x 36 9Mb SCD/DCD Sync Burst SRAMs |

| GS88236BD-150I | 512K x 18, 256K x 36 9Mb SCD/DCD Sync Burst SRAMs |

| GS88236BD-200 | 512K x 18, 256K x 36 9Mb SCD/DCD Sync Burst SRAMs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GS88218CB-200 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 2.5V/3.3V 9MBIT 512KX18 6.5NS/3NS 119FPBGA - Trays |

| GS88218CB-200I | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 2.5V/3.3V 9MBIT 512KX18 6.5NS/3NS 119FPBGA - Trays |

| GS88218CB-200IV | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V/2.5V 9MBIT 512KX18 6.5NS/3NS 119FPBGA - Trays |

| GS88218CB-200V | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V/2.5V 9MBIT 512KX18 6.5NS/3NS 119FPBGA - Trays |

| GS88218CB-250 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 2.5V/3.3V 9MBIT 512KX18 5.5NS/2.5NS 119FPBGA - Trays |

發布緊急采購,3分鐘左右您將得到回復。