- 您現在的位置:買賣IC網 > PDF目錄376314 > RM7000-250T (PMC-SIERRA INC) RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released PDF資料下載

參數資料

| 型號: | RM7000-250T |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| 中文描述: | 64-BIT, 250 MHz, RISC PROCESSOR, PBGA304 |

| 封裝: | 31 X 31 MM, TBGA-304 |

| 文件頁數: | 39/54頁 |

| 文件大小: | 901K |

| 代理商: | RM7000-250T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer

’

s Internal Use

Document ID: PMC-2002175, Issue 1

39

RM7000

Microprocessor with On-Chip Secondary Cache Datasheet

Released

5

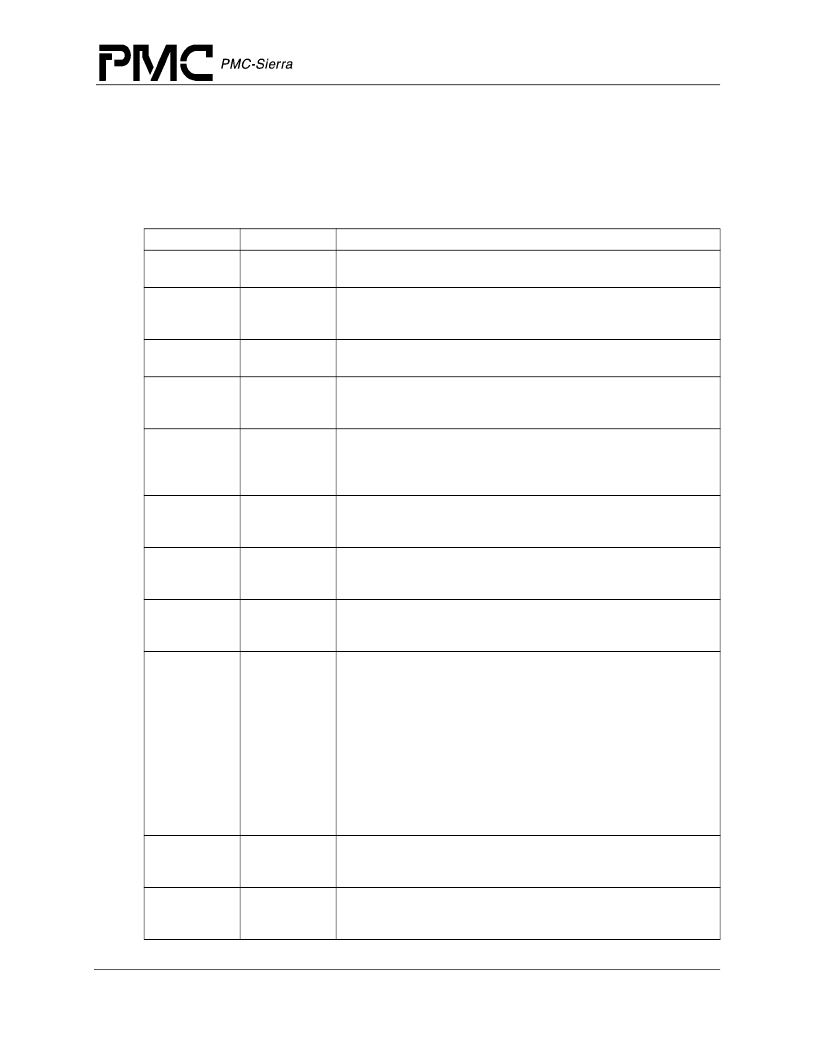

Pin Descriptions

The following is a list of control, data, clock, tertiary cache, interrupt, and miscellaneous pins of

the RM7000.

Table 17

System interface Pins

Pin Name

ExtRqst*

Type

Input

Description

External request

Signals that the system interface is submitting an external request.

Release interface

Signals that the processor is releasing the system interface to slave

state

Read Ready

Signals that an external agent can now accept a processor read.

Write Ready

Signals that an external agent can now accept a processor write

request.

Valid Input

Signals that an external agent is now driving a valid address or data on

the SysAD bus and a valid command or data identifier on the SysCmd

bus.

Valid output

Signals that the processor is now driving a valid address or data on the

SysAD bus and a valid command or data identifier on the SysCmd bus.

Processor Request

When asserted this signal requests that control of the system interface

be returned to the processor. This is enabled by Mode Bit 26.

Processor Acknowledge

When asserted, in response to PRqst*, this signal indicates to the

processor that it has been granted control of the system interface.

Response Swap

RspSwap* is used by the external agent to signal the processor when it

is about to return a memory reference out of order; i.e., of two

outstanding memory references, the data for the second reference is

being returned ahead of the data for the first reference. In order that the

processor will have time to switch the address to the tertiary cache, this

signal must be asserted a minimum of two cycles prior to the data itself

being presented. Note that this signal works as a toggle; i.e., for each

cycle that it is held asserted the order of return is reversed. By default,

anytime the processor issues a second read it is assumed that the

reads will be returned in order; i.e., no action is required if the reads are

indeed returned in order. This is enabled by Mode Bit 26.

Read Type

During the address cycle of a read request, RdType indicates whether

the read request is an instruction read or a data read.

System address/data bus

A 64-bit address and data bus for communication between the

processor and an external agent.

Release*

Output

RdRdy*

Input

WrRdy*

Input

ValidIn*

Input

ValidOut*

Output

PRqst*

Output

PAck*

Input

RspSwap*

Input

RdType

Output

SysAD(63:0)

Input/Output

相關PDF資料 |

PDF描述 |

|---|---|

| RM7000-263S | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7000-266T | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7000-300S | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7000-300T | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7935 | 64-bit Microprocessors with Integrated L2 Cache and EJTAG |

相關代理商/技術參數 |

參數描述 |

|---|---|

| RM7000263S | 制造商:QED 功能描述:* |

| RM7000-263S | 制造商:QED 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA 制造商:Quantum Effect Design 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA |

| RM7000-266T | 制造商:QED 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA |

| RM7000-300T | 制造商:QED 功能描述: 制造商:QED 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA |

| RM7000A | 制造商:PMC 制造商全稱:PMC 功能描述:64-Bit MIPS RISC Microprocessor with Integrated L2 Cache |

發布緊急采購,3分鐘左右您將得到回復。