- 您現在的位置:買賣IC網 > PDF目錄98217 > THS10064CDAR (TEXAS INSTRUMENTS INC) 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 PDF資料下載

參數資料

| 型號: | THS10064CDAR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| 封裝: | GREEN, PLASTIC, TSSOP-32 |

| 文件頁數: | 14/42頁 |

| 文件大小: | 527K |

| 代理商: | THS10064CDAR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

THS10064

SLAS255B – DECEMBER 1999 – REVISED DECEMBER 2002

www.ti.com

21

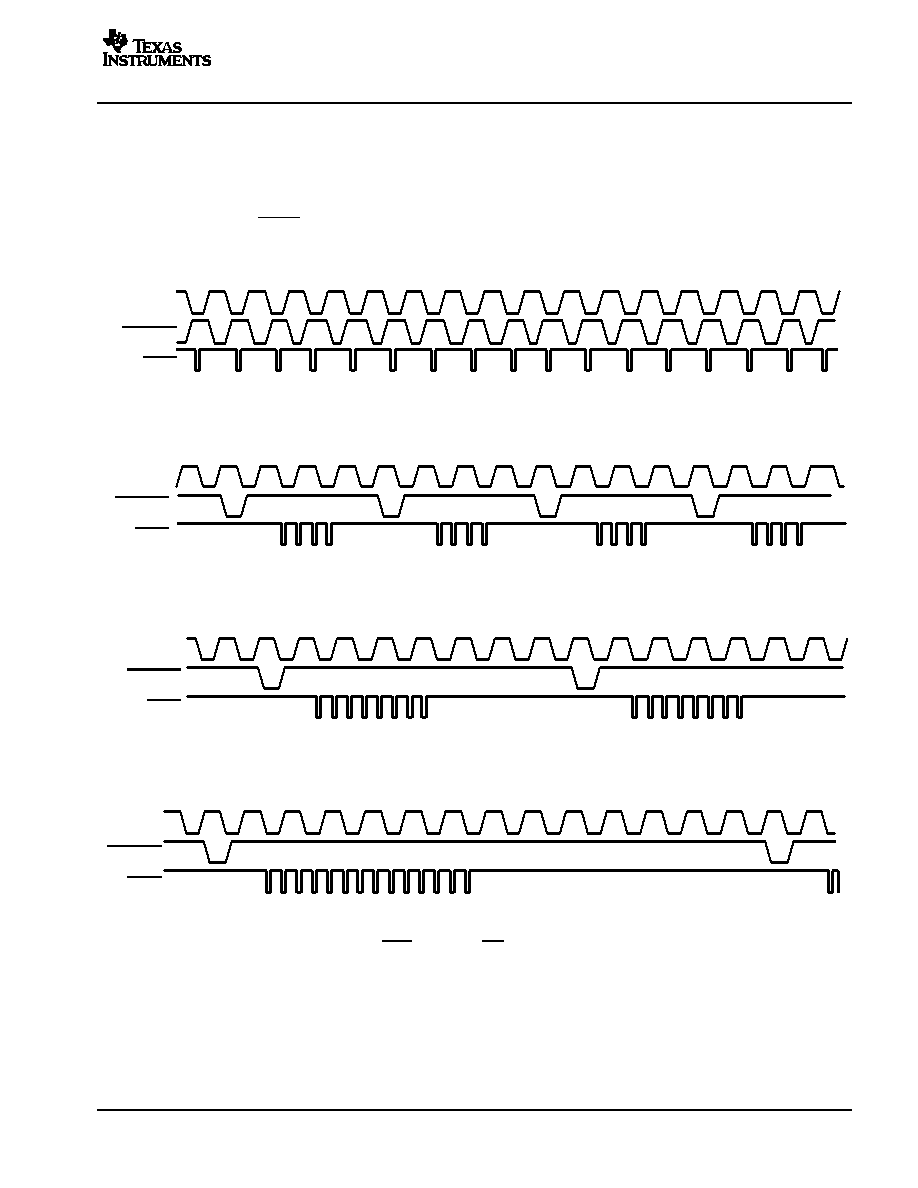

READING DATA FROM THE FIFO

The THS10064 informs the connected processor via the digital output DATA_AV (data available) that a block of

conversion values are ready to be read. The block size to be read is always equal to the setting of the trigger level.

The selectable trigger levels depend on the number of selected analog input channels. For example, when choosing

one analog input, a trigger level of 1, 4, 8, and 14 can be selected. The following figures demonstrate the principle

of reading the data (the READ signal is asynchronous to CONV_CLK).

In Figure 32, a trigger level of 1 is selected. The control signal DATA_AV is set to an active low pulse. This means

that the connected processor has the task to read 1 value from the ADC after every DATA_AV low pulse.

CONV_CLK

DATA_AV

READ

Figure 32. Trigger Level 1 Selected

In Figure 33, a trigger level of 4 is selected. The control signal DATA_AV is set to an active low pulse. This means

that the connected processor has the task to read 4 values from the ADC after every DATA_AV low pulse.

CONV_CLK

DATA_AV

READ

Figure 33. Trigger Level 4 Selected

In Figure 34, a trigger level of 8 is selected. The control signal DATA_AV is set to an active low pulse. This means

that the connected processor has the task to read 8 values from the ADC after every DATA_AV low pulse.

CONV_CLK

DATA_AV

READ

Figure 34. Trigger Level 8 Selected

In Figure 35, a trigger level of 14 is selected. The control signal DATA_AV is set to an active low pulse. This means

that the connected processor has the task to read 14 values from the ADC after every DATA_AV low pulse.

CONV_CLK

DATA_AV

READ

Figure 35. Trigger Level 14 Selected

READ is always the logical combination of CS0, CS1 and RD.

相關PDF資料 |

PDF描述 |

|---|---|

| THS10064IDAR | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS10064IDAG4 | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1007CDA | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1007CDAR | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1007CDAG4 | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| THS10064CDARG4 | 功能描述:模數轉換器 - ADC 10-Bit 6 MSPS Quad Ch DSP/uP Ifc RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS10064DA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT 6 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS10064EVM | 制造商:Texas Instruments 功能描述:THS10064 10-BIT, 6 MSPS, DC EVM - Bulk |

| THS10064IDA | 功能描述:模數轉換器 - ADC 10-Bit 6 MSPS Quad Ch DSP/uP Ifc RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS10064IDAG4 | 功能描述:模數轉換器 - ADC 10B 6 MSPS ADC Quad Ch. DSP/uP Interface RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發布緊急采購,3分鐘左右您將得到回復。