- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98229 > THS8083CPZP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | THS8083CPZP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | POWER, THERMALLY ENHANCED, PLASTIC, TQFP-100 |

| 文件頁數(shù): | 35/61頁 |

| 文件大小: | 266K |

| 代理商: | THS8083CPZP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

3–16

3.2.46 Register Name: CH2_RDBK

Subaddress: 33 (R)

CH2_RDBK7

MSB

LSB

CH2_RDBK6

CH2_RDBK5

CH2_RDBK4

CH2_RDBK3

CH2_RDBK2

CH2_RDBK1

CH2_RDBK0

CH2_RDBK[7..0]:

Readback register of ADC Channel 2

Default: (changed during operation)

3.2.47 Register Name: CH3_RDBK

Subaddress: 34 (R)

CH3_RDBK7

MSB

LSB

CH3_RDBK6

CH3_RDBK5

CH3_RDBK4

CH3_RDBK3

CH3_RDBK2

CH3_RDBK1

CH3_RDBK0

CH3_RDBK[7..0]:

Readback register of ADC Channel 3

Default: (changed during operation)

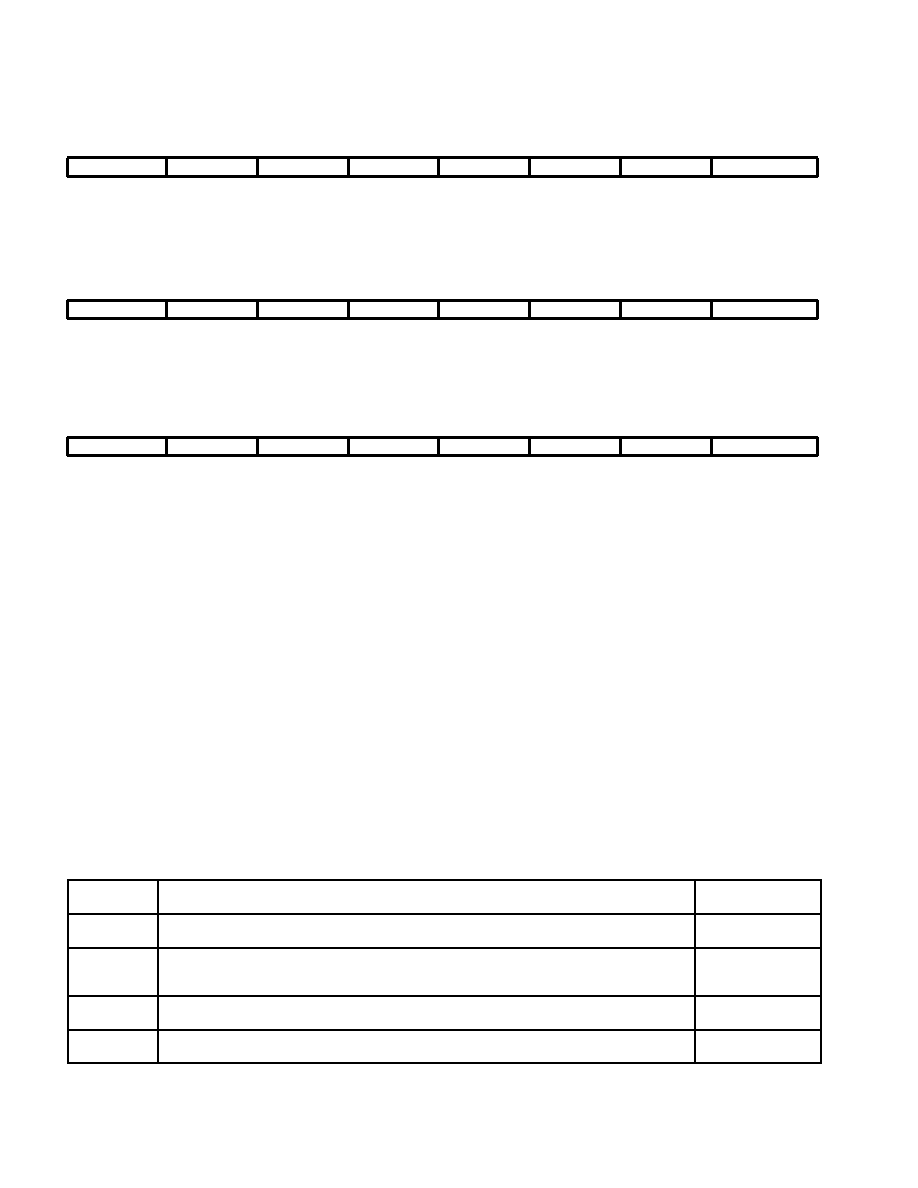

3.2.48 Register Name: OFM_CTRL

Subaddress: 40 (R/W)

X

MSB

LSB

X

DHS_MODE

DHS_POL

OFM_MODE1

OFM_MODE0

DHS_MODE

Controls how DHS (display horizontal sync output) is generated. DHS can be a version of the signal on the

HS input terminal, synchronized to the sampling clock and compensated for the data pipeline delay through

the part (see timing diagrams). This preserves the HS width but has the disadvantage that for some phase

settings there will be a one-pixel uncertainty on the exact timing of DHS (if HS falls within setup/hold time of

the input register that is clocked by the ADC sampling clock).

Therefore, a second option exist to generate DHS as the output pulse of the PLL feedback divider. Since this

pulse is generated once for every <TERM_CNT> cycles of the DTO clock, the uncertainty is resolved. This

can avoid possible horizontal line jitter on the display system. The width of the DHS pulse is in this case

always 1 ADC clock cycle, independent of the width of the incoming HS. This method also assures the

generation of a DHS pulse on every line, even when no incoming HS is present or when it is filtered out by

sync processing (e.g., from composite sync extraction).

0 = DHS is generated from the output of the PLL feedback divider (default)

1 = DHS is generated as a latched and delayed version of HS input

DHS_POL

Controls polarity of the DHS output

0 = positive polarity (default)

1 = negative polarity

OFM_MODE[1..0]:

Defines mode of output formatter and frequency on DATACLK1 as in Table 3–2.

Table 3–2. Output Formatter

OFM_MODE

[1..0]

DESCRIPTION

DATACLK1 OUT-

PUT FREQUENCY

00 (default)

24-bit parallel mode:

24-bit output on bus A, Bus B is Hi-Z

Fs

01

16-bit mode

16-bit output on ch1 and ch2 of bus A, with data from ch2 and ch3 downsampled by 2 (parallel 4:2:2

CCIR–601 mode), Bus B is Hi-Z

Fs

10

48-bit interleaved mode

48-bit output on buses A and B at half sampling rate. Data on bus B shifted by 1-Fs clock.

Fs/2

11

48-bit parallel mode

48-bit output on buses A and B at half sampling rate.

Fs/2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| THS8133ACPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133BCPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133BCPHPG4 | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133CPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8134BCPHP | PARALLEL, 8 BITS INPUT LOADING, 0.005 us SETTLING TIME, 8-BIT DAC, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS8083EVM | 制造商:Texas Instruments 功能描述:THS8083EVM - Bulk |

| THS8083T | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Triple 8-Bit, 80 MSPS, 3.3-V Video and Graphics Digitizer With Digital PLL |

| THS8-10R-D | 制造商:Thomas & Betts 功能描述:CATAMOUNT CABLE TIES |

| THS8133 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION WITH TRI-LEVEL SYNC GENERATION |

| THS8133_07 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION WITH TRI-LEVEL SYNC GENERATION |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。