- 您現在的位置:買賣IC網 > PDF目錄98246 > TLE7824G (INFINEON TECHNOLOGIES AG) SPECIALTY ANALOG CIRCUIT, PDSO28 PDF資料下載

參數資料

| 型號: | TLE7824G |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 元件分類: | 模擬信號調理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PDSO28 |

| 封裝: | GREEN, PLASTIC,SOP-28 |

| 文件頁數: | 52/53頁 |

| 文件大小: | 900K |

| 代理商: | TLE7824G |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當前第52頁第53頁

TLE7824G

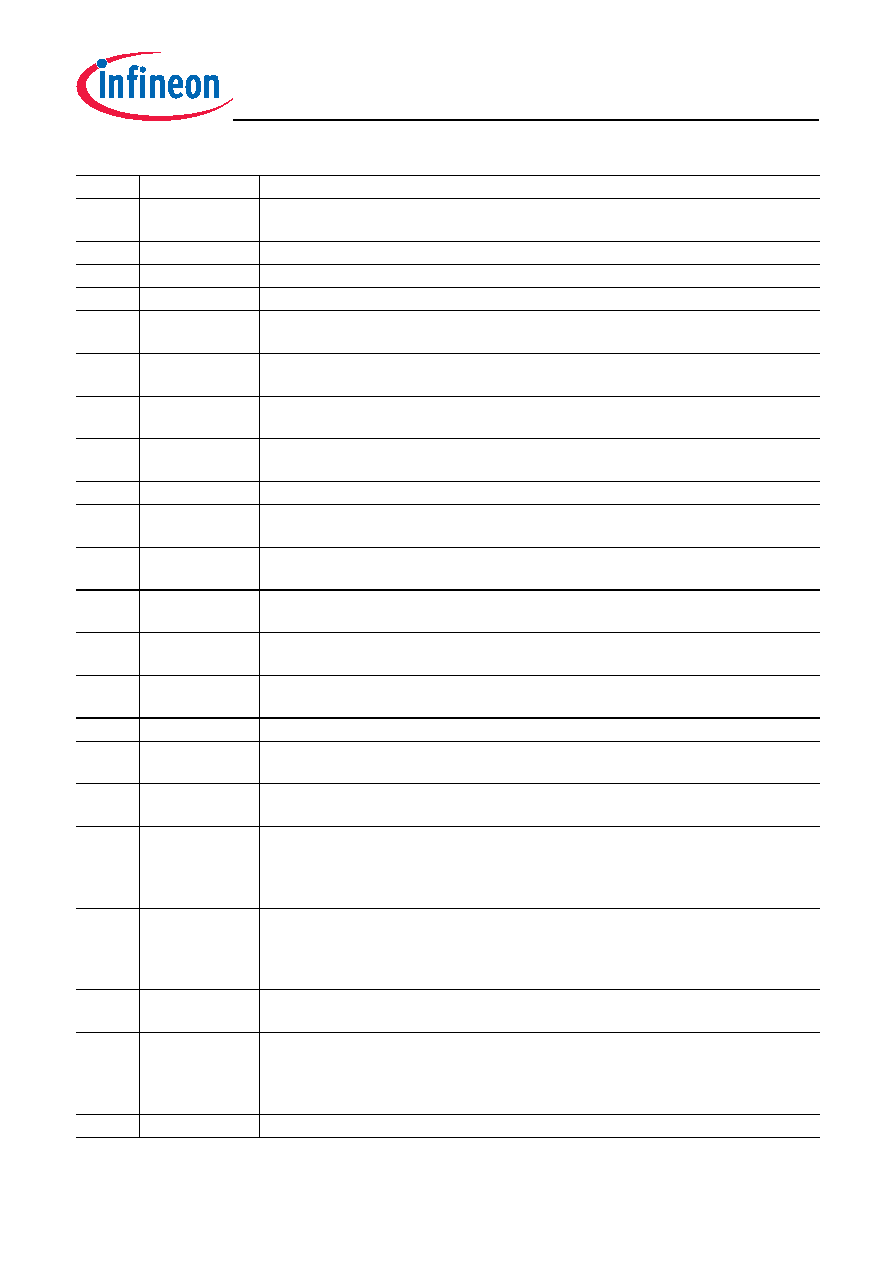

Pin Definitions and Functions

Data Sheet

8

Rev. 3.01, 2008-04-15

4LIN

LIN Bus; Bus Line for the LIN interface, according to ISO 9141 and LIN specification

1.3 and 2.0

24

SUPPLY

Supply Output; e.g. for Hall Sensor; controlled via SPI

5LS2

Low Side Switch 2 Output; controlled via SPI

6LS1

Low Side Switch 1 Output; controlled via SPI

9P0.3

General Purpose I/O with PWM Functionality

(alternate function: SCK, see XC885 data sheet)

10

P0.4

General Purpose I/O with Capture and PWM Functionality

(alternate function: MTSR, see XC885 data sheet)

11

P0.5

General Purpose I/O with PWM Functionality

(alternate function: MRST and EXINT0 ,see XC885 data sheet)

13

V

DDC

Voltage Regulator Output for

μController Core (2.5 V); for connection of block

capacitor to GND; not to be used for external loads

14

TMS

Test Mode Select (JTAG)

15

P0.0

[TCK_0]

General Purpose I/O; see XC885 data sheet

(alternate function: JTAG Clock Input)

16

P0.2

[TDO_0]

General Purpose I/O; see XC885 data sheet

(alternate function: JTAG Serial Data Output; RxD1)

17

P0.1

[TDI_0]

General Purpose I/O; see XC885 data sheet

(alternate function: JTAG Serial Data Input; TxD1)

18

P2.0

General Purpose Input (digital/analog) with Capture Functionality; e.g. for Hall

Sensor (alternate function: EXINT1)

19

P2.1

General Purpose Input (digital/analog) with Capture Functionality; e.g. for Hall

Sensor (alternate function: EXINT2)

20

V

DDP

Voltage Supply Input for

μController I/Os (5 V); to be connected with V

CC pin

–RxD

LIN Transceiver Data Output; according to the ISO 9141 and LIN specification 1.3

and 2.0; LOW in dominant state; connected to C General Purpose Input P1.0

–TxD

LIN Transceiver Data Input; according to ISO 9141 and LIN specification 1.3 and

2.0; TxD has an internal pull-up; connected to C General Purpose Input P1.1

–DI

SPI Data Input; receives serial data from the control device; serial data transmitted

to DI is a 16-bit control word with the Least Significant Bit (LSB) transferred first: the

input has a pull-down and requires CMOS logic level inputs; DI will accept data on

the falling edge of CLK-signal; connected to C General Purpose Input P1.3

–DO

SPI Data Output; this tri-state output transfers diagnosis data to the control device;

the output will remain in the high-impedance state unless the device is selected by a

low on Chip-Select-Not (CSN); connected to C General Purpose Input P1.4

(EXTINT0_1)

–CLK

SPI Clock Input; clock input for shift register; CLK has an internal pull-down and

requires CMOS logic level inputs; connected to C General Purpose Input P1.2

–CSN

SPI Chip Select Not Input; CSN is an active low input; serial communication is

enabled by pulling the CSN terminal low; CSN input should only be transitioned when

CLK is low; CSN has an internal pull-up and requires CMOS logic level inputs;

connected to C General Purpose Input P1.5

–

V

AREF

Voltage Reference for ADC

Pin No. Symbol

Function

相關PDF資料 |

PDF描述 |

|---|---|

| TLE8201R | SPECIALTY CONSUMER CIRCUIT, PDSO36 |

| TLE8242-2 | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| TLE8366EV33 | SWITCHING REGULATOR, PDSO8 |

| TLE8366EV50 | SWITCHING REGULATOR, PDSO8 |

| TLS2205DL | VOICE COIL MOTOR CONTROLLER, 1.4 A, PDSO48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLE7824GXUMA1 | 制造商:Infineon Technologies AG 功能描述:Low Side Switch, High Side/LED Driver 28-Pin DSO 制造商:Infineon Technologies AG 功能描述:EMBEDDED POWER - Tape and Reel 制造商:Infineon Technologies AG 功能描述:IC LDO VREG/LIN TXRX DSO-28 |

| TLE7826G | 功能描述:功率驅動器IC EMBEDDED POWER RoHS:否 制造商:Micrel 產品:MOSFET Gate Drivers 類型:Low Cost High or Low Side MOSFET Driver 上升時間: 下降時間: 電源電壓-最大:30 V 電源電壓-最小:2.75 V 電源電流: 最大功率耗散: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube |

| TLE7826GXUMA1 | 制造商:Infineon Technologies AG 功能描述:Low Side Switch, High Side/LED Driver 28-Pin DSO 制造商:Infineon Technologies AG 功能描述:EMBEDDED POWER - Tape and Reel 制造商:Infineon Technologies AG 功能描述:IC LDO VREG/LIN TXRX DSO-28 |

| TLE8080EMXUMA1 | 制造商:Infineon Technologies AG 功能描述:ENGINECONTR_SMALL_ENGINE - Tape and Reel |

| TLE8088EMXUMA1 | 制造商:Infineon Technologies AG 功能描述:ENGINECONTR_SMALL_ENGINE - Tape and Reel |

發布緊急采購,3分鐘左右您將得到回復。