- 您現在的位置:買賣IC網 > PDF目錄98293 > TS83102G0BCGL (E2V TECHNOLOGIES PLC) 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 PDF資料下載

參數資料

| 型號: | TS83102G0BCGL |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 |

| 封裝: | 21 X 21 MM, 1.27 MM PITCH, CERAMIC, BGA-152 |

| 文件頁數: | 3/60頁 |

| 文件大小: | 1510K |

| 代理商: | TS83102G0BCGL |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

11

0830E–BDC–06/07

e2v semiconductors SAS 2007

TS83102G0B

Note:

Output error amplitude < ±6 LSB, Fs = 2 Gsps, T

J = 110°C

7. See “Definition of Terms” on page 34.

8. 50

// C

LOAD = 2 pF termination (for each single-ended output). Termination load parasitic capacitance derating value:

50 ps/pF (ECL). See “Timing Information” on page 36.

9. TOD and TDR propagation times are defined at package input/outputs. They are given for reference only. See “Propagation

10. Values for TD1 and TD2 are given for a 2 Gsps external clock frequency (50% duty cycle). For different sampling rates, apply

the following formula: TD1 = T/2 + (|TOD - TDR|) and TD2 = T/2 + (|TOD - TDR|), where T = clock period. This places the ris-

ing edge (True/False) of the differential data ready signal in the middle of the output data valid window. This gives maximum

setup and hold times for external data acquisition.

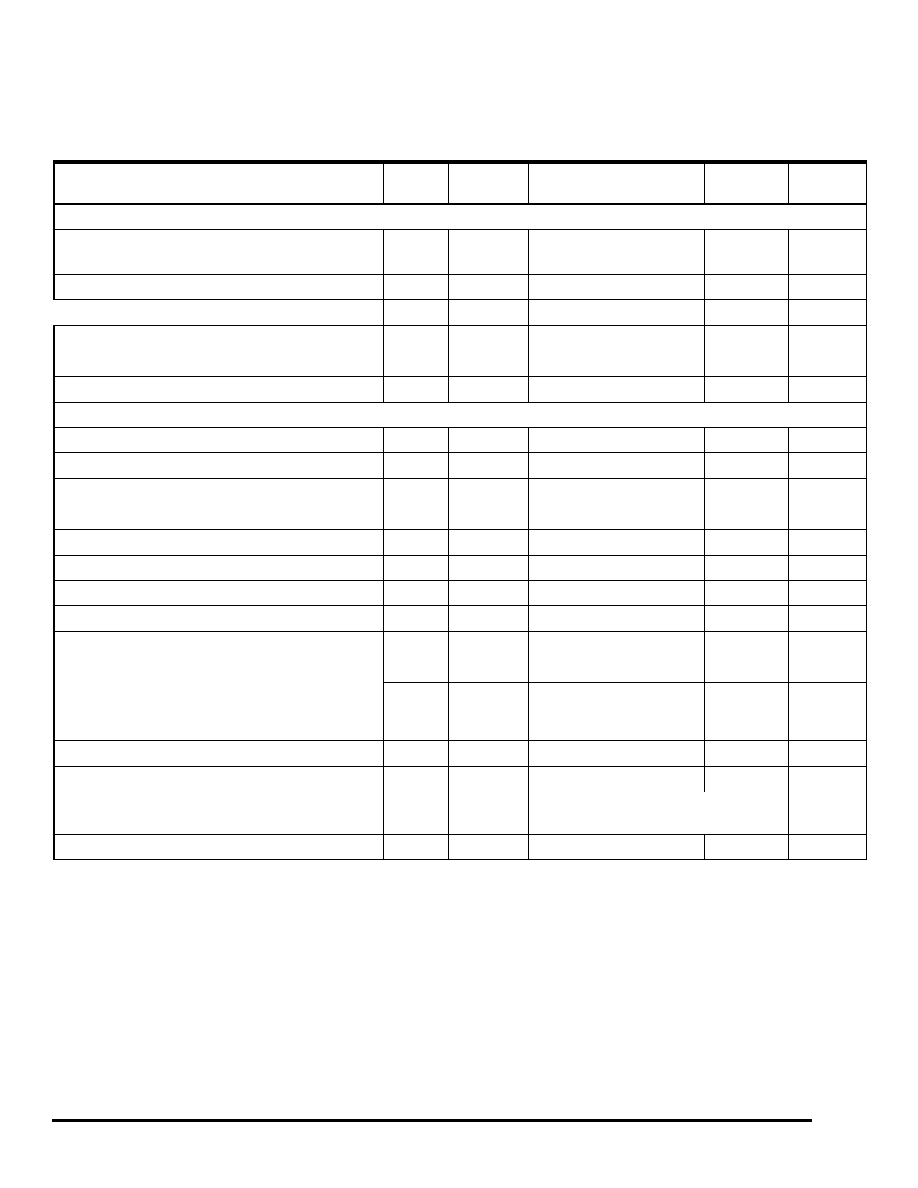

7.6

Transient and Switching Performances

Parameter

Test

Level

Symbol

Min

Typ

Max

Unit

Transient Performance

Bit error rate (Note:)

4

BER

10-12

Error/

sample

ADC setting time (VIN - VINB = 400 mVpp)

4

TS

1

ns

Overvoltage recovery time

4

ORT

500

ps

ADC step response rise/fall time (10 - 90%)

80

100

ps

Overshoot

4%

Ringback

2%

Switching Performance and Characteristics

Maximum clock frequency (7)

FSMax

2

2.2

Gsps

Minimum clock frequency (7)

4F

SMin

150

200

Msps

Minimum clock pulse width (high)

4

TC1

0.2

0.25

2.5

ns

Minimum clock pulse width (low)

4

TC2

0.2

0.25

2.5

ns

Aperture delay (7)

4

TA

160

ps

Aperture uncertainty (7)

4

Jitter

150

200

fs rms

Output rise/fall time for DATA (20 - 80%) (8)

4

TR/TF

150

200

ps

Output rise/fall time for DATA READY (20 - 80%) (8)

4

TR/TF

150

200

ps

Data output delay (9)

4

TOD

360

ps

Data ready output delay (9)

4

TDR

410

ps

4

ITOD

minus

TDRI

050

100

ps

Output data to data ready propagation delay (10)

4

TD1

250

300

350

ps

Data ready to output data propagation delay (10)

4

TD2

150

200

250

ps

Output data pipeline delay

4

TPD

4.0

Clock

cycles

Data ready reset delay

4

TRDR

1000

ps

相關PDF資料 |

PDF描述 |

|---|---|

| TS83110CZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110VZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZB/T | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDSO28 |

| TS83110VS | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TS83102G0BVGL | 制造商:e2v technologies 功能描述:ADC SGL 2GSPS 10-BIT PARALLEL 152CBGA - Trays |

| TS83102G0CGL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog to Digital Converter |

| TS83102G0GSZR5 | 制造商:e2v technologies 功能描述:TS83102G0GSZR5 - Trays |

| TS831-3I | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:MICROPOWER VOLTAGE SUPERVISOR RESET ACTIVE LOW |

| TS831-3ID | 功能描述:監控電路 2.71V Micropower AL RoHS:否 制造商:STMicroelectronics 監測電壓數: 監測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復位:Resettable 監視器:No Watchdog 電池備用開關:No Backup 上電復位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。