- 您現在的位置:買賣IC網 > PDF目錄98293 > TS83102G0BCGL (E2V TECHNOLOGIES PLC) 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 PDF資料下載

參數資料

| 型號: | TS83102G0BCGL |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 |

| 封裝: | 21 X 21 MM, 1.27 MM PITCH, CERAMIC, BGA-152 |

| 文件頁數: | 30/60頁 |

| 文件大小: | 1510K |

| 代理商: | TS83102G0BCGL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

36

0830E–BDC–06/07

TS83102G0B

e2v semiconductors SAS 2007

13. TS83102G0B Operating Features

13.1

Timing Information

13.1.1

Timing Value for TS83102G0B

The timing values are defined in the “Electrical Operating Characteristics” on page 5.

The timing values are given at the package inputs/outputs, taking into account the package’s transmis-

sion line, bond wire, pad and ESD protections capacitance, as well as specified termination loads. The

evaluation board propagation delays in 50

controlled impedance traces are not taken into account.

You should apply proper derating values corresponding to termination topology.

13.1.2

Propagation Time Considerations

The TOD and TDR timing values are given from the package pin to pin and do not include the additional

propagation times between the device pins and input/output termination loads. For the evaluation board,

the propagation time delay is 6.1 ps/mm (155 ps/inch) corresponding to a 3.4 dielectric constant (at 10

GHz) of the RO4003 used for the board.

If a different dielectric layer is used (for instance Teflon), you should use appropriate propagation time

values.

TD1 and TD2 do not depend on propagation times because they are differential data (see “Definition of

TD1 and TD2 are also the most straightforward data to measure, because they are differential: TD can

be measured directly on the termination loads, with matching oscilloscope probes.

13.1.3

TOD-TDR Variation Over Temperature

Values for TOD and TDR track each other over the temperature (there is a 1% variation for TOD and

TDR per 100

°C temperature variation). Therefore the TOD and TDR variation over temperature is negli-

gible. Moreover, the internal (on-chip) skews between each TOD and TDR data effect can be considered

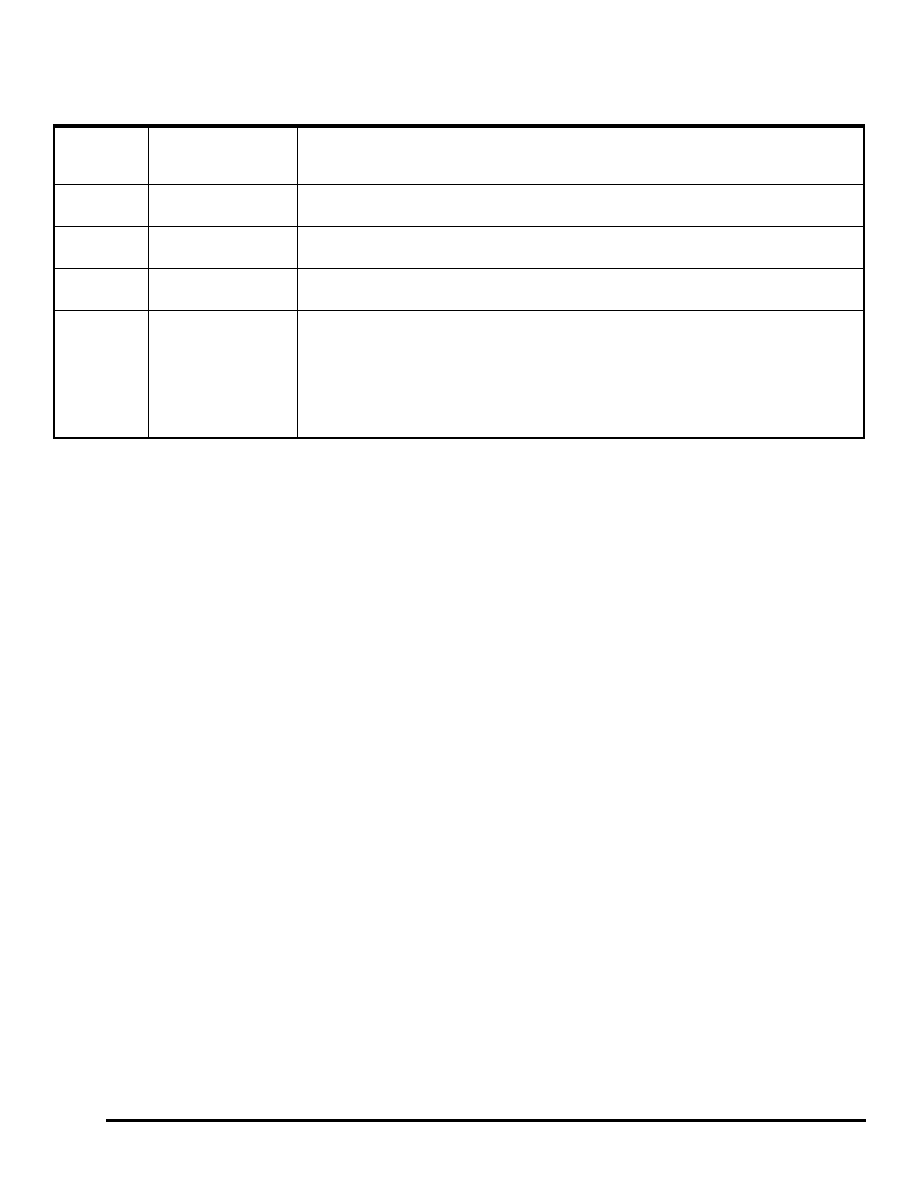

TPD

Pipeline Delay

The number of clock cycles between the sampling edge of an input data and the associated

output data being made available (not taking in account the TOD). For the JTS8388B the

TPD is 4 clock periods

TR

Rise Time

Time delay for the output data signals to rise from 20% to 80% of delta between the low level

and high level

TRDR

Data Ready Reset

Delay

Delay between the falling edge of the Data Ready output asynchronous Reset signal

(DDRB) and the reset to digital zero transition of the Data Ready output signal (DR)

TS

Settling Time

Time delay to achieve 0.2% accuracy at the converter output when an 80% full-scale step

function is applied to the differential analog input

VSWR

Voltage Standing

Wave

Where S11 is the reflection coefficient of the scattering

matrix. The VSWR over frequency measures the degree of

mismatching between the packaged ADC input impedance (ideally 50

or so) and the

transmission line’s impedance. The packaged ADC input impedance (transmission line and

termination) is controlled so as to ensure VSWR < 1.2 :1 from DC up to 2.5 GHz. A VSWR of

1.2 :1 corresponds to a 0.039 dB insertion loss (20 dB return loss) - i.e. 99% power

transmitted and 1% reflected

Table 12-1.

Definitions of Terms (Continued)

VSWR

1

S11

+

()

1

S11

–

()

÷

=

相關PDF資料 |

PDF描述 |

|---|---|

| TS83110CZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110VZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZB/T | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDSO28 |

| TS83110VS | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TS83102G0BVGL | 制造商:e2v technologies 功能描述:ADC SGL 2GSPS 10-BIT PARALLEL 152CBGA - Trays |

| TS83102G0CGL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog to Digital Converter |

| TS83102G0GSZR5 | 制造商:e2v technologies 功能描述:TS83102G0GSZR5 - Trays |

| TS831-3I | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:MICROPOWER VOLTAGE SUPERVISOR RESET ACTIVE LOW |

| TS831-3ID | 功能描述:監控電路 2.71V Micropower AL RoHS:否 制造商:STMicroelectronics 監測電壓數: 監測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復位:Resettable 監視器:No Watchdog 電池備用開關:No Backup 上電復位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。