- 您現在的位置:買賣IC網 > PDF目錄365968 > TSB14C01HV (Texas Instruments, Inc.) 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER PDF資料下載

參數資料

| 型號: | TSB14C01HV |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| 中文描述: | 5V的電機及電子學工程師聯合會1394-1995背板收發器/仲裁者 |

| 文件頁數: | 15/35頁 |

| 文件大小: | 224K |

| 代理商: | TSB14C01HV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

3

–

3

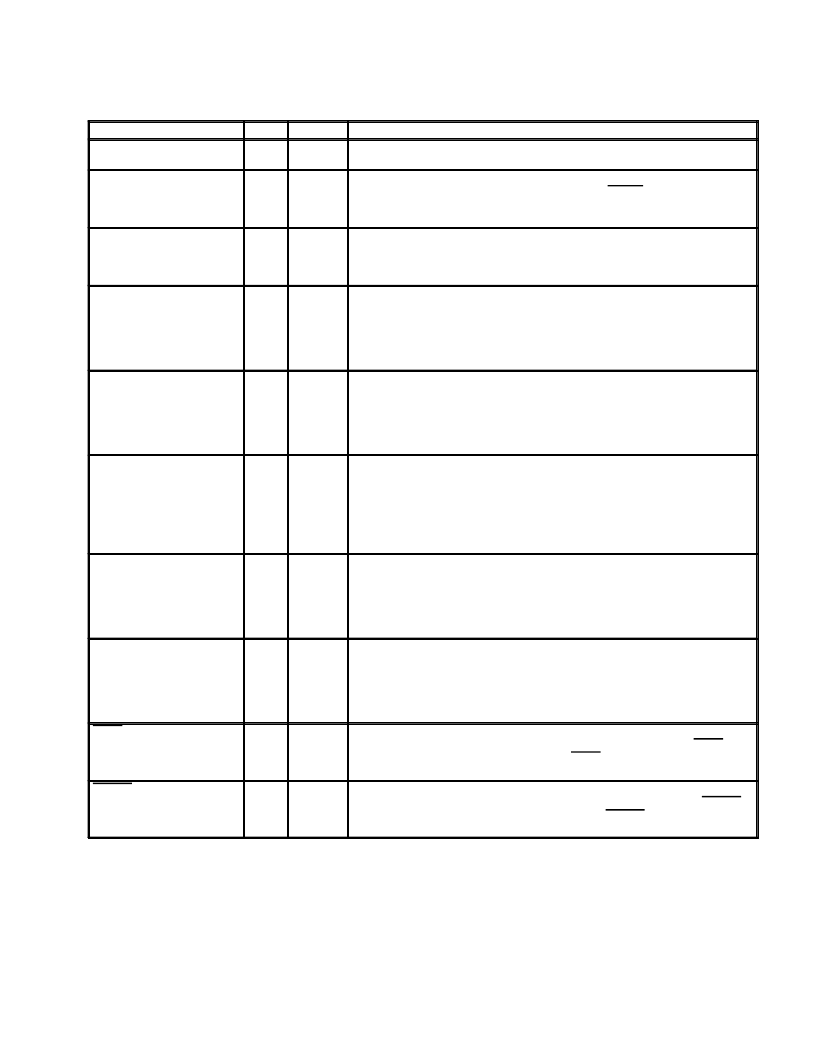

Table 3-2. Base Register Field Description (Continued)

FIELD

SIZE

TYPE

DESCRIPTION

SMRST

1

R/W

State machine reset. When this bit is written to, TSB14AA1A first clears, then resets all

state machines in the PHY. This bit is self-clearing. The power-up state of this field is 0b.

SWHRST

1

R/W

Software initiate hardware reset. When this bit is set to 1, TSB14AA1A performs a reset

of the same nature as the reset caused by toggling the RESET pin on the device. This

clears all state machines and register settings to their power-on reset states. This bit is

self-clearing. The power-up state of this field is 0b.

LAST_ARB_WON_PRIORITY

4

R

Priority code of physical layer node that last won arbitration. This field contains the

priority used by the node that last won the arbitration process on the bus. It is only valid

when the E bit is 1. This field is supplied for system debug purposes. The power-up state

of this field is 0b.

DDLS

1

R/W

Drive data line state. When the M_TEST pin is asserted (high) and the ENDLS bit is set

to 1, the TSB14AA1A drives the state of the DDLS bit on the TDATA output pin of the

device. This mode of operation is for diagnostic testing only. It is not a valid 1394

operating mode and will not allow proper 1394 bus operation if connected to a 1394 bus.

The power-up state of this bit is 0b. The state of this bit is not affected by bus resets or

state machine resets. This bit is cleared upon HW or SWHRST reset.

DSLS

1

R/W

Drive strobe line state. When the M_TEST pin is asserted (high) and the ENDLS bit is

set to 1, the TSB14AA1A drives the state of the DSLS bit on the TSTRB output pin of the

device. This mode of operation is for diagnostic testing only. It is not a valid 1394

operation mode and will not allow proper 1394 bus operation if connected to a 1394 bus.

The power-up state of this bit is 0b. The state of this bit is not affected by bus resets or

state machine resets. This bit is cleared upon hardware or SWHRST reset.

ENDLS

1

R/W

Enable drive line state. When the M_TEST pin is asserted (high) and ENDLS is set to 1,

the TSB14AA1A drives the state of the DDLS bit on the TDATA output pin of the device.

It also drives the state of the DSLS bit on the TSTRB output pin of the device. This mode

of operation is for diagnostic testing only. It is not a valid 1394 operation mode and will

not allow proper 1394 bus operation if connected to a 1394 bus. The power-up state of

this bit is 0b. The state of this bit is not affected by bus resets or state machine resets.

This bit is cleared upon hardware or SWHRST reset.

TDATA

1

R

Transmitted data line state. When the E bit is 1, the line state read from this field is valid.

This bit reads 1 for a data line 1 (logical 1) being transmitted by the TSB14AA1A and 0

for a data line 0 (logical 0). The power-up state of this field is 0b. This bit is updated on a

best effort basis. TDATA is not required to be toggled with every change of the TDATA

output pin. It can be expected to be updated at least every 9 SCLKs, the length of the

register read LREQ.

TSTRB

1

R

Transmit strobe line state. When the E bit is 1, the line state read from this field is valid.

This bit reads 1 for a strobe line 1 (logical 1) being transmitted by the TSB14AA1A and 0

for a strobe line 0 (logical 0). The power-up state of this field is 0b. This bit is updated on a

best effort basis. TSTRB is not required to be toggled with every change of the TSTRB

output pin. It can be expected to be updated at least every 9 SCLKs, the length of the

register read LREQ.

TDOE

1

R

3-State output enable. When the E bit is 1, the state read from this field is valid. The

power-up state of this field is 0b. This bit is updated on a best effort basis. TDOE is not

required to be toggled with every change of the TDOE output pin. It can be expected to

be updated at least every 9 SCLKs, the length of the register read LREQ.

OCDOE

1

R

Open collector output enable. When the E bit is 1, the state read from this field is valid.

The power-up state of this field is 0b. This bit is updated on a best effort basis. OCDOE is

not required to be toggled with every change of the OCDOE output pin. It can be

expected to be updated at least every 9 SCLKs, the length of the register read LREQ.

相關PDF資料 |

PDF描述 |

|---|---|

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB2203X6MMX30M | IC APEX 20KE FPGA 200K 240-PQFP |

| TSB2204.5X12MMX20M | IC APEX 20KE FPGA 200K 240-PQFP |

| TSB2204.5X19MMX20M | IC APEX 20KE FPGA 200K 240-PQFP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSB14C01MHV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Transceiver |

| TSB14C01PM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EURO TERMINAL BLOCKS |

| TSB150002DS | 制造商:TE Connectivity 功能描述: |

| TSB150004DS | 制造商:TE Connectivity 功能描述:Conn Europa Terminal Blocks 8 POS 13.5mm Screw ST Cable Mount 40A/Contact |

發布緊急采購,3分鐘左右您將得到回復。