- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9864BCPZ (ANALOG DEVICES INC) IF Digitizing Subsystem PDF資料下載

參數資料

| 型號: | AD9864BCPZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | IF Digitizing Subsystem |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, QCC48 |

| 封裝: | LEAD FREE, MO-220VKKD-2, LFCSP-48 |

| 文件頁數: | 22/44頁 |

| 文件大小: | 1984K |

| 代理商: | AD9864BCPZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

AD9864

SSI OUTPUT DRIVE STRENGTH SETTING

2

14

4

N

12

3

1

7

7

6

5

24-BIT I/O DATA

13

11

9

10

8

16-BIT I/O DATA

w/DVGA ENABLED

16-BIT I/O DATA

0

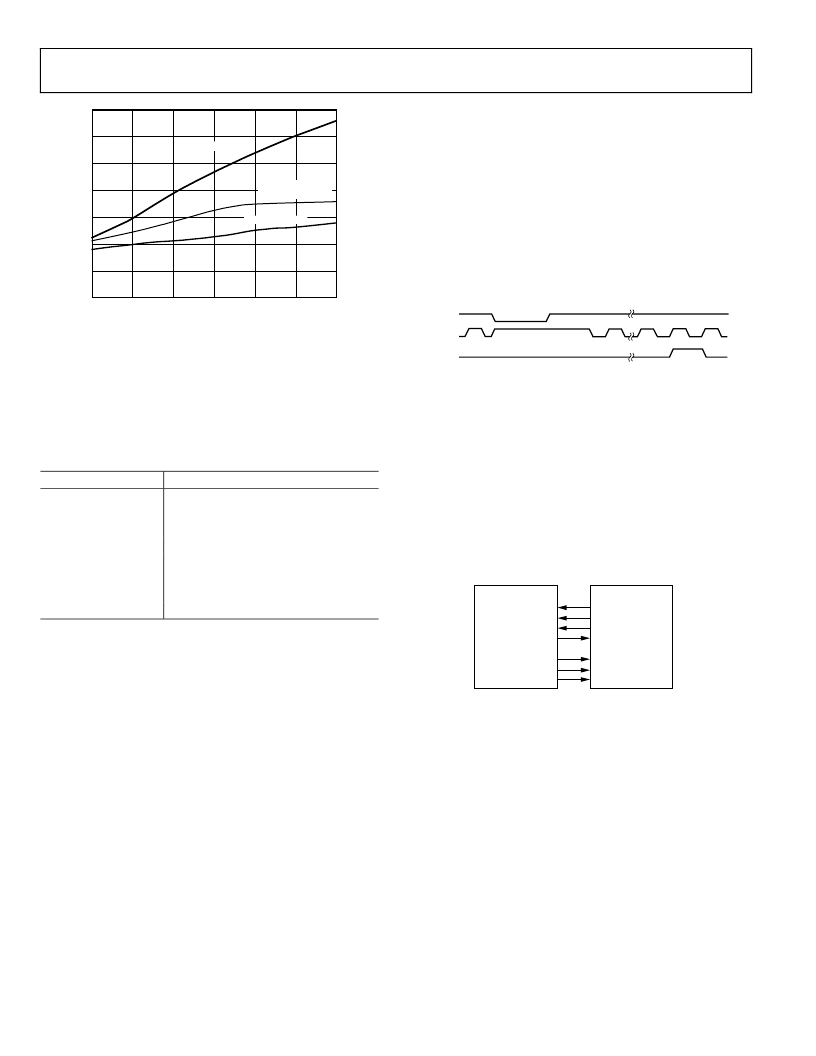

Figure 35. NF vs. SSI Output Drive Strength

(VDDx = 3.0 V, F

CLK

= 18 MSPS, BW = 75 kHz)

Table 10 lists the typical output rise/fall times as a function of DS

for a 10 pF load. Rise/fall times for other capacitor loads can be

determined by multiplying the typical values presented by a scal-

ing factor equal to the desired capacitive load divided by 10 pF.

Table 10. Typical Rise/Fall Times (±25%) with a 10 pF

Capacitive Load for Each DS Setting

DS

Typ (ns)

0

13.5

1

7.2

2

50

3

3.7

4

3.2

5

2.8

6

2.3

7

2.0

SYNCRONIZATION USING SYNCB

Many applications require the ability to synchronize one or

more AD9864s in a way that causes the output data to be pre-

cisely aligned to an external asynchronous signal. For example,

receiver applications employing diversity often require syn-

chronization of multiple AD9864s’ digital outputs. Satellite

communication applications using TDMA methods may

require synchronization between payload bursts to compensate

for reference frequency drift and Doppler effects.

SYNCB can be used for this purpose. It is an active-low signal

that clears the clock counters in both the decimation filter and

the SSI port. The counters in the clock synthesizers are not reset

because it is presumed that the CLK signals of multiple chips

would be connected. SYNCB also resets the modulator, result-

ing in a large-scale impulse that must propagate through the

AD9864’s digital filter and SSI data formatting circuitry before

recovering valid output data. As a result, data samples unaf-

fected by this SYNCB induced impulse can be recovered 12

output data samples after SYNCB goes high (independent of

the decimation factor).

Figure 36 shows the timing relationship between SYNCB and

the SSI port’s CLKOUT and FS signals. SYNCB is an asynchro-

nous active-low signal that must remain low for at least half an

input clock period, i.e., 1/(2 × f

CLK

). CLKOUT remains high

while FS remains low upon SYNCB going low. CLKOUT will

become active within one to two output clock periods upon

SYNCB returning high. FS will reappear several output cycles

later, depending on the digital filter’s decimation factor and the

SSIORD setting. Note that for any decimation factor and

SSIORD setting, this delay is fixed and repeatable. To verify

proper synchronization, the FS signals of the multiple AD9864

devices should be monitored.

FS

SYNCB

CLKOUT

0

Figure 36.

SYNCB Timing

INTERFACING TO DSPs

The AD9864 connects directly to an Analog Devices program-

mable digital signal processor (DSP). Figure 37 illustrates an

example with the Blackfin series of ADSP-2153x processors.

The Blackfin DSP series of 16-bit products is optimized for

telecommunications applications with its dynamic power man-

agement feature, making it well suited for portable radio prod-

ucts. The code compatible family members share the funda-

mental core attributes of high performance, low power con-

sumption, and the ease-of-use advantages of a microcontroller

instruction set.

AD9864

CLKOUT

RSCLK

RFS

R

PC

PE

PD

SCK

SEL

MOSI

ISO

DOUTBM

FS

DOUTAD

SPI

SSI

ADSP-2153x

SERIAL

PORT

SPI-PORT

0

Figure 37. Example of AD9864 and ADSP-2153x Interface

As shown in Figure 37,

AD9864’s synchronous serial interface

(SSI) links the receive data stream to the DSP’s serial port

(SPORT). For AD9864 setup and register programming, the

device connects directly to ADSP-2153x’s SPI port. Dedicated

select lines (SEL) allow the ADSP-2153x to program and read

back registers of multiple devices using only one SPI port. The

DSP driver code pertaining to this interface is available on the

AD9864 Web page.

Rev. 0 | Page 22 of 44

相關PDF資料 |

PDF描述 |

|---|---|

| AD9864BCPZRL | IF Digitizing Subsystem |

| AD9866BCPRL | Broadband Modem Mixed Signal Front End |

| AD9866CHIPS | Broadband Modem Mixed Signal Front End |

| AD9866 | Broadband Modem Mixed Signal Front End |

| AD9866-EB | Broadband Modem Mixed Signal Front End |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9864BCPZ | 制造商:Analog Devices 功能描述:IC, IF SUBSYSTEM, 16-24BIT, 6.8KHZ-270KH |

| AD9864BCPZRL | 功能描述:IC IF SUBSYSTEM GEN-PURP 48LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9864-EB | 制造商:Analog Devices 功能描述: |

| AD9864-EBZ | 功能描述:BOARD EVAL FOR AD9864 制造商:analog devices inc. 系列:- 零件狀態:有效 類型:數字轉換器 頻率:10MHz ~ 300MHz 配套使用產品/相關產品:AD9864 所含物品:板 標準包裝:1 |

| AD9865 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

發布緊急采購,3分鐘左右您將得到回復。