- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9864BCPZ (ANALOG DEVICES INC) IF Digitizing Subsystem PDF資料下載

參數資料

| 型號: | AD9864BCPZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | IF Digitizing Subsystem |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, QCC48 |

| 封裝: | LEAD FREE, MO-220VKKD-2, LFCSP-48 |

| 文件頁數: | 38/44頁 |

| 文件大小: | 1984K |

| 代理商: | AD9864BCPZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當前第38頁第39頁第40頁第41頁第42頁第43頁第44頁

AD9864

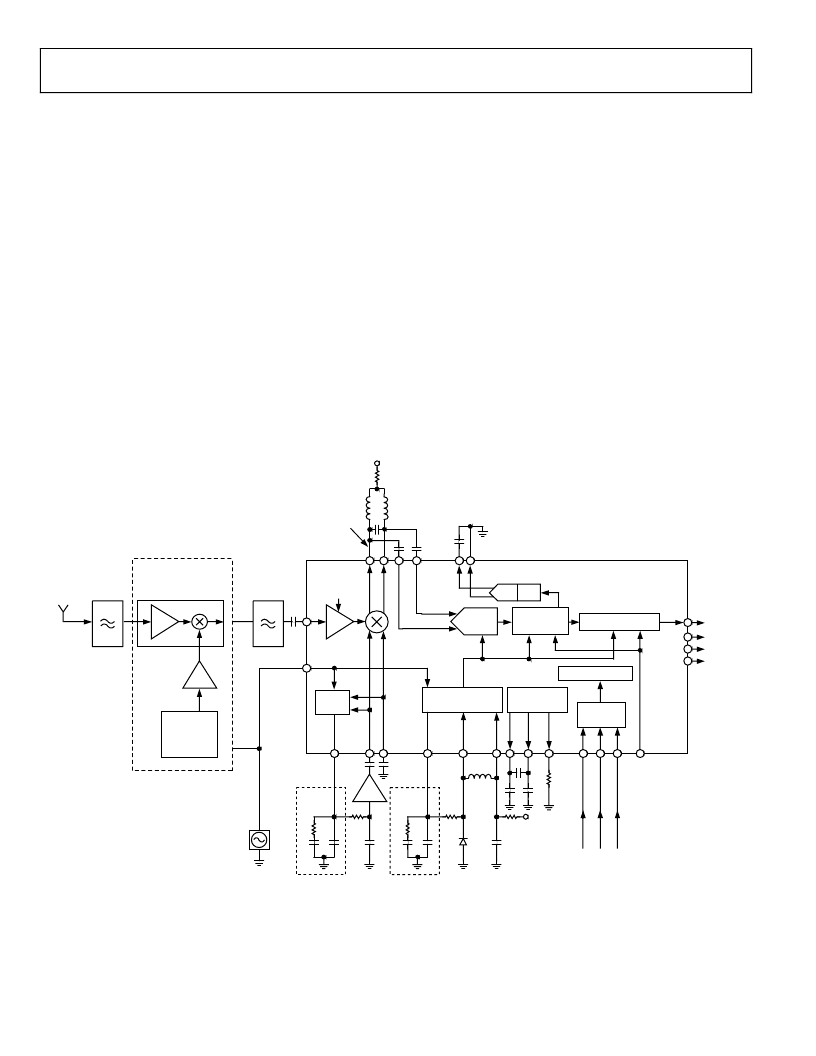

The LO, CLK, and IFIN signals are coupled to their respective

inputs using 10 nF capacitors. The output of the mixer is cou-

pled to the input of the ADC using 100 pF. An external 100 k

resistor from the RREF pin to GND sets up the AD9864’s

internal bias currents. VREFP and VREFN provide a differen-

tial reference voltage to the AD9864’s Σ- ADC and must be

decoupled by a 0.01 μF differential capacitor along with two

100 pF capacitors to GND. The remaining capacitors are used

to decouple other sensitive internal nodes to GND.

Although power supply decoupling capacitors are not shown, it

is recommended that a 0.1 μF surface-mount capacitor be

placed as close as possible to each power supply pin for maxi-

mum effectiveness. Also not shown is the input impedance

matching network used to match the AD9864’s IF input to the

external IF filter. Lastly, the loop filter components associated

with the LO and CLK synthesizers are not shown.

LC component values for

f

CLK

= 18 MHz are given Figure 70.

For other clock frequencies, the two inductors and the capaci-

tor of the LC tank should be scaled in inverse proportion to the

clock. For example, if

f

CLK

= 26 MHz, the two inductors should

be = 6.9 μH and the capacitor should be about 120 pF. A toler-

ance of 10% is sufficient for these components since tuning of

the LC tank is performed upon system startup.

APPLICATIONS

SuperHeterodyne Receiver Example

The AD9864 is well suited for analog and/or digital narrow-band

radio systems based on a superheterodyne receiver architecture. The

superheterodyne architecture is noted for achieving exceptional

dynamic range and selectivity by using two or more downconversion

stages to provide amplification of the target signal while filtering the

undesired signals. The AD9864 greatly simplifies the design of these

radio systems by integrating the complete IF strip (excluding the LO

VCO) while providing an I/Q digital output (along with other sys-

tem parameters) for the demodulation of both analog and digital

modulated signals. The AD9864’s exceptional dynamic range often

simplifies the IF filtering requirements and eliminates the need for an

external AGC.

RF

INPUT

PRESELECT

FILTER

TUNER

IF CRYSTAL OR

SAW FILTER

VDDA

Σ

-

ADC

LNA

VCO

ADF42xx

PLL SYN

REFIN

TO

DSP

AD9864

DECIMATION

FILTER

SAMPLE CLOCK

SYNTHESIZER

I

LOOP

FILTER

L

L

VCO

LOOP

FILTER

VDDC

I

C

C

FROM DSP

LO

SYNTH.

VOLTAGE

REFERENCE

SPI

R

V

V

S

P

P

P

CRYSTAL

OSCILLATOR

IFIN

–16dB

LNA

V

V

I

I

DAC AGC

FORMATTING/SSI

DOUTA

DOUTB

FS

CLKOUT

CONTROL LOGIC

G

G

IF2 =

f

CLK

/8

0

Figure 71. Typical Dual Conversion Superheterodyne Application Using the AD9864

Rev. 0 | Page 38 of 44

相關PDF資料 |

PDF描述 |

|---|---|

| AD9864BCPZRL | IF Digitizing Subsystem |

| AD9866BCPRL | Broadband Modem Mixed Signal Front End |

| AD9866CHIPS | Broadband Modem Mixed Signal Front End |

| AD9866 | Broadband Modem Mixed Signal Front End |

| AD9866-EB | Broadband Modem Mixed Signal Front End |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9864BCPZ | 制造商:Analog Devices 功能描述:IC, IF SUBSYSTEM, 16-24BIT, 6.8KHZ-270KH |

| AD9864BCPZRL | 功能描述:IC IF SUBSYSTEM GEN-PURP 48LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9864-EB | 制造商:Analog Devices 功能描述: |

| AD9864-EBZ | 功能描述:BOARD EVAL FOR AD9864 制造商:analog devices inc. 系列:- 零件狀態:有效 類型:數字轉換器 頻率:10MHz ~ 300MHz 配套使用產品/相關產品:AD9864 所含物品:板 標準包裝:1 |

| AD9865 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

發布緊急采購,3分鐘左右您將得到回復。