- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373970 > AD9876 (Analog Devices, Inc.) Broadband Modem Mixed-Signal Front End PDF資料下載

參數(shù)資料

| 型號(hào): | AD9876 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 模擬前端 |

| 英文描述: | Broadband Modem Mixed-Signal Front End |

| 中文描述: | 寬帶調(diào)制解調(diào)器混合信號(hào)前端 |

| 文件頁(yè)數(shù): | 2/24頁(yè) |

| 文件大小: | 666K |

| 代理商: | AD9876 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

REV. A

–2–

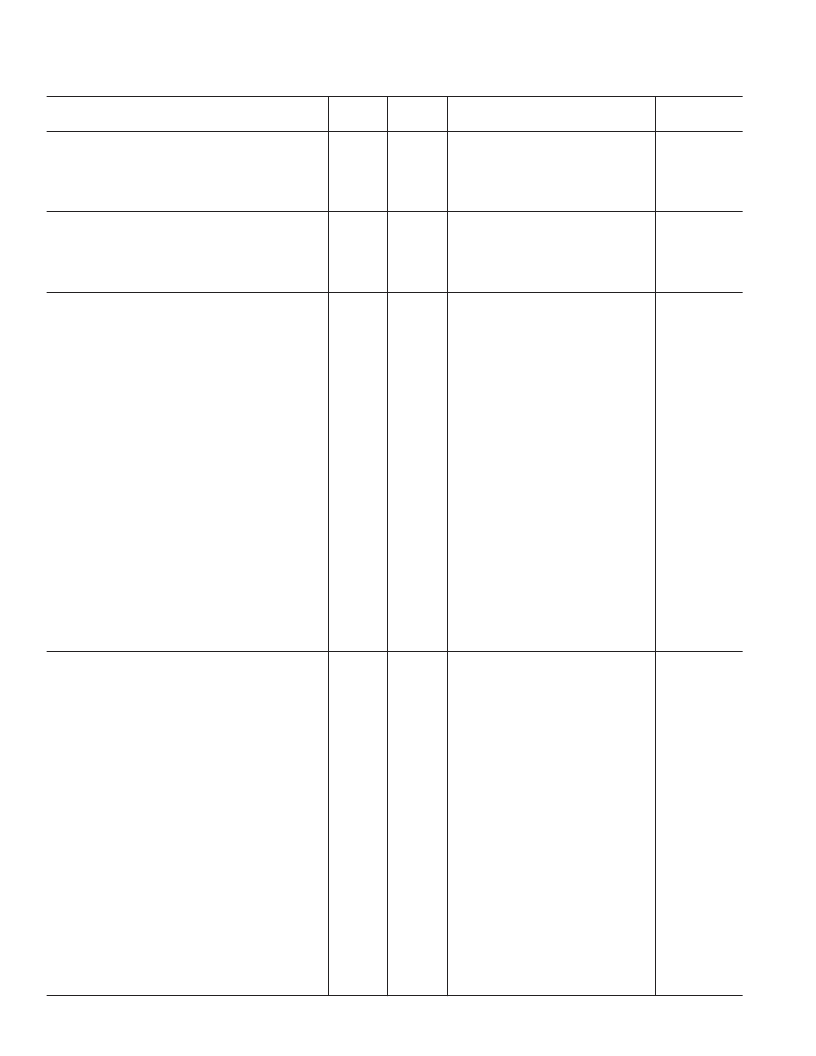

AD9876–SPECIFICATIONS

Test

Level

Parameter

Temp

Min

Typ

Max

Unit

OSCIN CHARACTERISTICS

Frequency Range

Duty Cycle

Input Capacitance

Input Impedance

Full

Full

25

°

C

25

°

C

II

II

III

III

10

40

64

60

MHz

%

pF

M

50

3

100

CLOCK OUTPUT CHARACTERISTICS

CLK A Jitter (f

CLKA

Derived from PLL)

CLK A Duty Cycle

CLK B Jitter (f

CLKB

Derived from PLL)

CLK B Duty Cycle

25

°

C

25

°

C

25

°

C

25

°

C

III

III

III

III

14

50

±

5

33

50

±

5

ps rms

%

ps rms

%

Tx CHARACTERISTICS

Tx Path Latency, 4

×

Interpolation

Interpolation Filter Bandwidth (–0.1 dB)

4

×

Interpolation, LPF

2

×

Interpolation, LPF

TxDAC

Resolution

Conversion Rate

Full-Scale Output Current

Voltage Compliance Range

Gain Error

Output Offset (Single-Ended)

Differential Nonlinearity

Integral Nonlinearity

Output Capacitance

Phase Noise @ 1 kHz Offset, 10 MHz Signal

Signal-to-Noise and Distortion (SINAD)

10 MHz Analog Out AD9876 (20 MHz BW)

Wideband SFDR (to Nyquist, 64 MHz Max)

5 MHz Analog Out

10 MHz Analog Out

Narrow-Band SFDR (3 MHz Window):

10 MHz Analog Out

IMD (f1 = 6.9 MHz, f2 = 7.1 MHz)

Full

II

86

f

DAC

Cycles

Full

Full

II

II

13

26

MHz

MHz

Full

Full

Full

Full

Full

Full

Full

25

°

C

25

°

C

25

°

C

II

II

II

II

II

II

III

III

III

III

12

Bits

MHz

mA

V

% FS

μ

A

LSB

LSB

pF

dBc/Hz

10

2

–0.5

–5

0

128

20

+1.5

+5

5

10

±

2

2

±

1

±

2

5

–100

Full

25

°

C

25

°

C

25

°

C

I

III

III

III

62.5

65

dB

80

74

dBc

dBc

25

°

C

25

°

C

III

III

88

–80

dBc

dBFS

Rx PATH CHARACTERISTICS

Resolution

Conversion Rate

Pipeline Delay, ADC Clock Cycles

DC Accuracy

Differential Nonlinearity

Integral Nonlinearity

Dynamic Performance (ADC Clocked Direct)

(A

IN

= –0.5 dBFS, f = 5 MHz)

@ f

OSCIN

= 32 MHz

Signal-to-Noise and Distortion Ratio (SINAD)

Effective Number of Bits (ENOB)

Signal-to-Noise Ratio (SNR)

Total Harmonic Distortion (THD)

Spurious-Free Dynamic Range (SFDR)

Dynamic Performance (ADC Clocked, PLLB/2)

(

A

IN

= –0.5 dBFS, f = 5 MHz

)

@ F

PLLB/2

= 50 MHz

Signal-to-Noise and Distortion Ratio (SINAD)

Effective Number of Bits (ENOB)

Signal-to-Noise Ratio (SNR)

Total Harmonic Distortion (THD)

Spurious-Free Dynamic Range (SFDR)

NA

Full

NA

NA

II

NA

12

Bits

MHz

Cycles

7.5

64

5.5

Full

Full

II

II

–1.0

–4.5

±

0.25

±

0.5

+1.0

+3.5

LSB

LSB

Full

Full

25

°

C

25

°

C

25

°

C

I

I

III

III

III

60.8

9.8

63.2

10.2

64

–70

72

dB

Bits

dB

dB

dB

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

III

III

III

III

III

56

9.3

59

–63

68

dB

Bits

dB

dB

dB

(V

S

= 3.3 V 10%, f

OSCIN

= 32 MHz, f

DAC

= 128 MHz, Gain = –6 dB, R

SET

= 4.02 k ,

100

DAC single-ended load, unless otherwise noted. )

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9876-EB | Broadband Modem Mixed-Signal Front End |

| AD9876BST | Broadband Modem Mixed-Signal Front End |

| AD9876BSTRL | Broadband Modem Mixed-Signal Front End |

| AD9877 | Mixed-Signal Front End Set-Top Box, Cable Modem |

| AD9877ABS | Mixed-Signal Front End Set-Top Box, Cable Modem |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9876ABST | 制造商:Rochester Electronics LLC 功能描述:12B BROADBAND MODEM MXFE CONVERTER - Tape and Reel 制造商:Analog Devices 功能描述: |

| AD9876ABSTRL | 制造商:Rochester Electronics LLC 功能描述:12B BROADBAND MODEM MXFE CONVERTER - Tape and Reel 制造商:Analog Devices 功能描述: |

| AD9876BST | 制造商:Analog Devices 功能描述:Modem Chip Single 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:12B BROADBAND MODEM MXFE CONVERTER - Bulk |

| AD9876BSTRL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD9876EB | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。