- 您現在的位置:買賣IC網 > PDF目錄373970 > AD9876 (Analog Devices, Inc.) Broadband Modem Mixed-Signal Front End PDF資料下載

參數資料

| 型號: | AD9876 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 模擬前端 |

| 英文描述: | Broadband Modem Mixed-Signal Front End |

| 中文描述: | 寬帶調制解調器混合信號前端 |

| 文件頁數: | 3/24頁 |

| 文件大小: | 666K |

| 代理商: | AD9876 |

REV. A

–3–

AD9876

Test

Level

Parameter

Temp

Min

Typ

Max

Unit

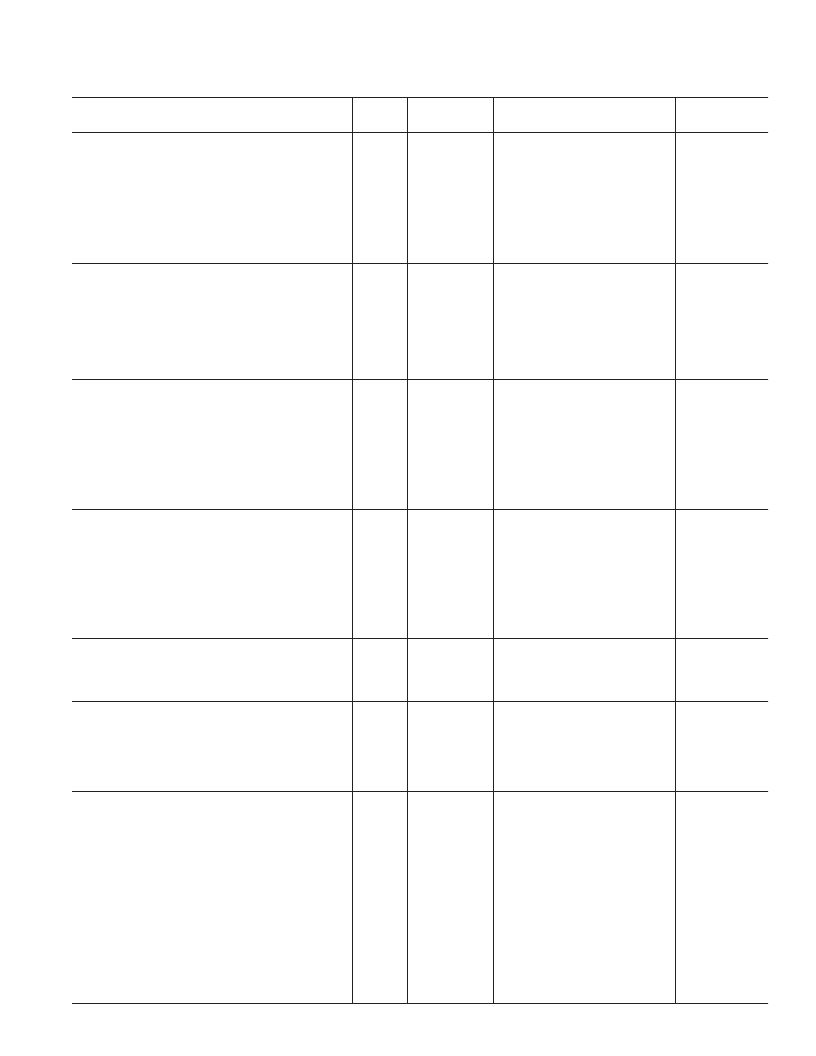

Rx PATH GAIN/OFFSET

Minimum Programmable Gain

Maximum Programmable Gain (12 MHz Filter)

Maximum Programmable Gain (26 MHz Filter)

Gain Step Size

Gain Step Accuracy

Gain Range Error

Offset Error, PGA Gain = 0 dB

Absolute Gain Error

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

III

III

III

III

III

III

III

III

–6

36

30

2

±

0.4

±

1.0

±

10

±

0.8

dB

dB

dB

dB

dB

dB

LSB

dB

Rx PATH INPUT CHARACTERISTICS

Input Voltage Range

Input Capacitance

Differential Input Resistance

Input Bandwidth (–3 dB)

Input Referred Noise (at –36 dB Gain with Filter)

Input Referred Noise (at –6 dB Gain with Filter)

Common-Mode Rejection

Rx PATH LPF (Low Cutoff Frequency)

Cutoff Frequency

Cutoff Frequency Variation

Attenuation @ 22 MHz

Pass-Band Ripple

Group Delay Variation

Settling Time

(to 1% FS, Min to Max Gain Change)

Total Harmonic Distortion at Max Gain (THD)

Rx PATH LPF (High Cutoff Frequency)

Cutoff Frequency

Cutoff Frequency Variation

Attenuation @ 44 MHz

Pass-Band Ripple

Group Delay Variation

Settling Time

(to 1% FS, Min to Max Gain Change)

Total Harmonic Distortion at Max Gain (THD)

Rx PATH DIGITAL HPF

Latency (ADC Clock Source Cycles)

Roll-Off in Stop Band

–3 dB Frequency

Full

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

III

III

III

III

III

III

III

4

4

270

50

16

684

40

Vppd

pF

MHz

μ

V rms

μ

V rms

dB

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

III

III

III

III

III

12

±

7

20

±

1.0

30

MHz

%

dB

dB

ns

25

°

C

25

°

C

III

III

150

–68

ns

dBc

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

III

III

III

III

III

26

±

7

20

±

1.2

15

MHz

%

dB

dB

ns

25

°

C

25

°

C

III

III

80

–65

ns

dBc

Full

Full

Full

II

II

II

1

6

f

ADC

/400

Cycle

dB/Octave

Hz

Rx PATH DISTORTION PERFORMANCE

IMD: f1 = 6.5 MHz, f2 = 7.7 MHz

12 MHz Filter: 0 dB Gain

: 30 dB Gain

26 MHz Filter: 0 dB Gain

: 30 dB Gain

25

°

C

25

°

C

25

°

C

25

°

C

III

III

III

III

–65

–57

–65

–56

dBc

dBc

dBc

dBc

POWER-DOWN/DISABLE TIMING

DAC I

OUT

OFF after Tx QUIET Asserted

DAC I

ON after Tx QUIET De-Asserted

Power-Down Delay (Active to Power-Down)

DAC

Interpolator

Power-Up Delay (Power-Down to Active)

DAC

PLL

ADC

PGA

LPF

Interpolator

VRC

Minimum RESET Pulsewidth Low (t

RL

)

Full

Full

II

II

200

1

ns

μ

s

Full

Full

II

II

400

200

ns

ns

Full

Full

Full

Full

Full

Full

Full

Full

II

II

II

II

II

II

II

II

40

10

1000

1

1

200

2

5

μ

s

μ

s

μ

s

μ

s

μ

s

ns

μ

s

f

OSCIN

Cycles

相關PDF資料 |

PDF描述 |

|---|---|

| AD9876-EB | Broadband Modem Mixed-Signal Front End |

| AD9876BST | Broadband Modem Mixed-Signal Front End |

| AD9876BSTRL | Broadband Modem Mixed-Signal Front End |

| AD9877 | Mixed-Signal Front End Set-Top Box, Cable Modem |

| AD9877ABS | Mixed-Signal Front End Set-Top Box, Cable Modem |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9876ABST | 制造商:Rochester Electronics LLC 功能描述:12B BROADBAND MODEM MXFE CONVERTER - Tape and Reel 制造商:Analog Devices 功能描述: |

| AD9876ABSTRL | 制造商:Rochester Electronics LLC 功能描述:12B BROADBAND MODEM MXFE CONVERTER - Tape and Reel 制造商:Analog Devices 功能描述: |

| AD9876BST | 制造商:Analog Devices 功能描述:Modem Chip Single 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:12B BROADBAND MODEM MXFE CONVERTER - Bulk |

| AD9876BSTRL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD9876EB | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。