- 您現在的位置:買賣IC網 > PDF目錄373972 > AD9957_07 (Analog Devices, Inc.) 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC PDF資料下載

參數資料

| 型號: | AD9957_07 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| 中文描述: | 1 GSPS的正交數字上變頻器與18位智商數據路徑和14位DAC |

| 文件頁數: | 5/60頁 |

| 文件大小: | 840K |

| 代理商: | AD9957_07 |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

AD9957

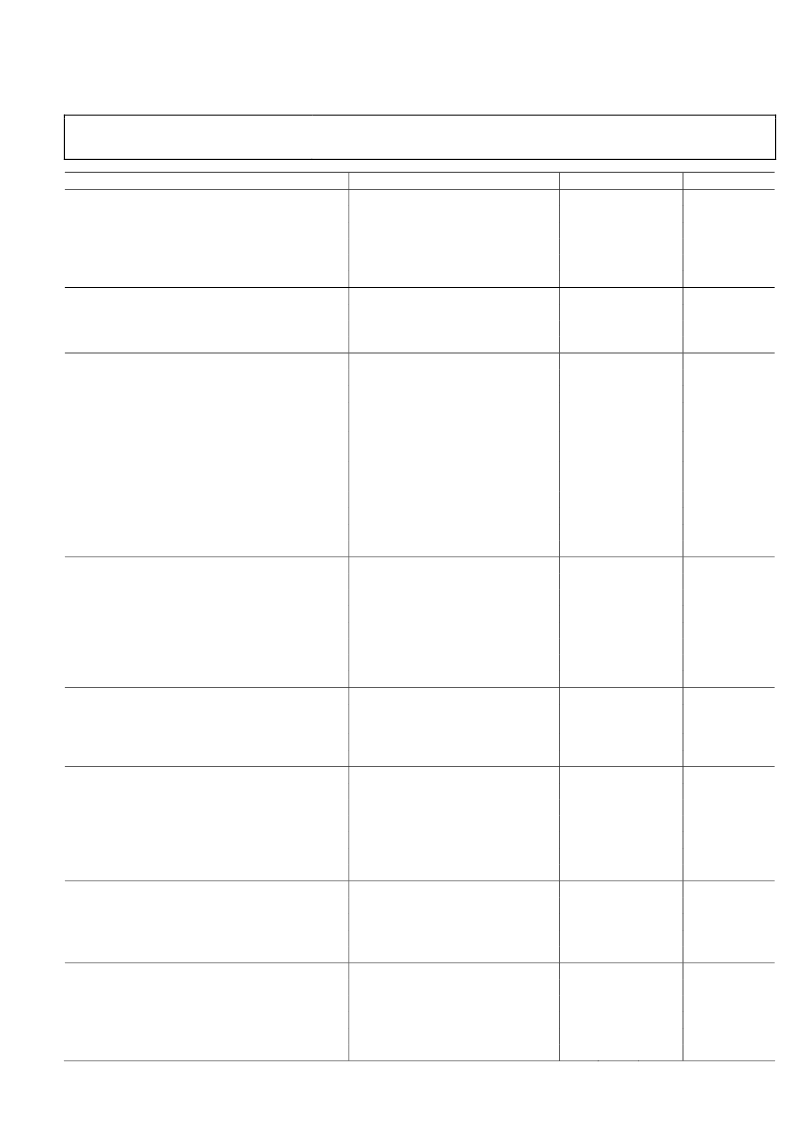

Parameter

NOISE SPECTRAL DENSITY (NSD)

Single Tone

f

OUT

= 20.1 MHz

f

OUT

= 98.6 MHz

f

OUT

= 201.1 MHz

f

OUT

= 397.8 MHz

TWO-TONE INTERMODULATION DISTORTION (IMD)

f

OUT

= 25 MHz

f

OUT

= 50 MHz

f

OUT

= 100 MHz

MODULATOR CHARACTERISTICS

Input Data

Error Vector Magnitude

Rev. 0 | Page 5 of 60

Test Conditions/Comments

I/Q rate = 62.2 MSPS; 16× interpolation

2.5 Msymbols/s, QPSK, 4× oversampled

270.8333 ksymbols/s, GMSK, 32×

oversampled

2.5 Msymbols/s 256-QAM, 4×

oversampled

Min

Typ

167

162

157

151

82

78

73

0.53

0.77

Max

Unit

dBm/Hz

dBm/Hz

dBm/Hz

dBm/Hz

dBc

dBc

dBc

%

%

0.35

%

WCDMA FDD (TM1), 3.84 MHz Bandwidth,

5 MHz Channel Spacing

Adjacent Channel Leakage Ratio (ACLR)

Carrier Feedthrough

SERIAL PORT TIMING CHARACTERISTICS

Maximum SCLK Frequency

Minimum SCLK Pulse Width

Maximum SCLK Rise/Fall Time

Minimum Data Setup Time to SCLK

Minimum Data Hold Time to SCLK

Maximum Data Valid Time in Read Mode

IO_UPDATE/PS0/PS1/PS2/RT TIMING CHARACTERISTICS

Minimum Pulse Width

IF = 143.88 MHz

Low

High

High

4

4

5

0

1

78

78

70

2

11

dBc

dBc

Mbps

ns

ns

ns

ns

ns

ns

SYNC_CLK

cycle

ns

ns

MHz

ns

ns

ns

ns

SYSCLK cycles

μs

SYSCLK cycles

4

SYSCLK cycles

SYSCLK cycles

Minimum Setup Time to SYNC_CLK

Minimum Hold Time to SYNC_CLK

IQ INPUT TIMING CHARACTERISTICS

Maximum PDCLK Frequency

Minimum IQ Data Setup Time to PDCLK

Minimum IQ Data Hold Time to PDCLK

Minimum TX_ENABLE Setup Time to PDCLK

Minimum TX_ENABLE Hold Time to PDCLK

Minimum TX_ENABLE Pulse Width

MISCELLANEOUS TIMING CHARACTERISTICS

Wake-Up Time

3

Fast Recovery Mode

Full Sleep Mode

Minimum Reset Pulse Width High

DATA LATENCY (PIPELINE DELAY)

Data Latency Single Tone Mode

Frequency, Phase, Amplitude-to-DAC Output

Frequency, Phase-to-DAC Output

Matched latency enabled

Matched latency disabled

2

2

1

2

1

250

1

8

5

91

79

0

150

相關PDF資料 |

PDF描述 |

|---|---|

| AD9958BCPZ-REEL7 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958BCPZ | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9970 | 14-Bit CCD Signal Processor with Precision Timing Generator |

| AD9971 | 12-Bit CCD Signal Processor with Precision Timing |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9957BCPZ | 制造商:Analog Devices 功能描述:GSPS QUADRATURE DIGITAL UPCONVERTER W/18-BIT IQ DATA PATH - Trays |

| AD9957BSVZ | 功能描述:IC DDS 1GSPS 14BIT IQ 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9957BSVZ-REEL | 功能描述:IC DDS 1GSPS 14BIT IQ 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9957BSVZREEL13 | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Quadrature Digital Upconverter w/18-Bit IQ Data Path and 14-Bit DAC |

| AD9958 | 制造商:AD 制造商全稱:Analog Devices 功能描述:2-Channel 500 MSPS DDS with 10-Bit DACs |

發布緊急采購,3分鐘左右您將得到回復。