- 您現在的位置:買賣IC網 > PDF目錄374033 > ADSP-21364 (Analog Devices, Inc.) SHARC Processor PDF資料下載

參數資料

| 型號: | ADSP-21364 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 數字信號處理 |

| 英文描述: | SHARC Processor |

| 中文描述: | SHARC處理器 |

| 文件頁數: | 6/52頁 |

| 文件大小: | 853K |

| 代理商: | ADSP-21364 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Rev. PrB

|

Page 6 of 52

|

September 2004

ADSP-21364

Preliminary Technical Data

Using the DM bus and PM buses, with one dedicated to each

memory block assures single-cycle execution with two data

transfers. In this case, the instruction must be available in the

cache.

DMA Controller

The ADSP-21364’s on-chip DMA controller allows data trans-

fers without processor intervention. The DMA controller

operates independently and invisibly to the processor core,

allowing DMA operations to occur while the core is simulta-

neously executing its program instructions. DMA transfers can

occur between the ADSP-21364’s internal memory and its serial

ports, the SPI-compatible (Serial Peripheral Interface) ports, the

IDP (Input Data Port), the Parallel Data Acquisition Port

(PDAP), or the parallel port. Twenty-five channels of DMA are

available on the ADSP-21364—two for the SPI interface, two for

memory-to-memory transfers, twelve via the serial ports, eight

via the Input Data Port, and one via the processor’s parallel

port. Programs can be downloaded to the ADSP-21364 using

DMA transfers. Other DMA features include interrupt genera-

tion upon completion of DMA transfers, and DMA chaining for

automatic linked DMA transfers.

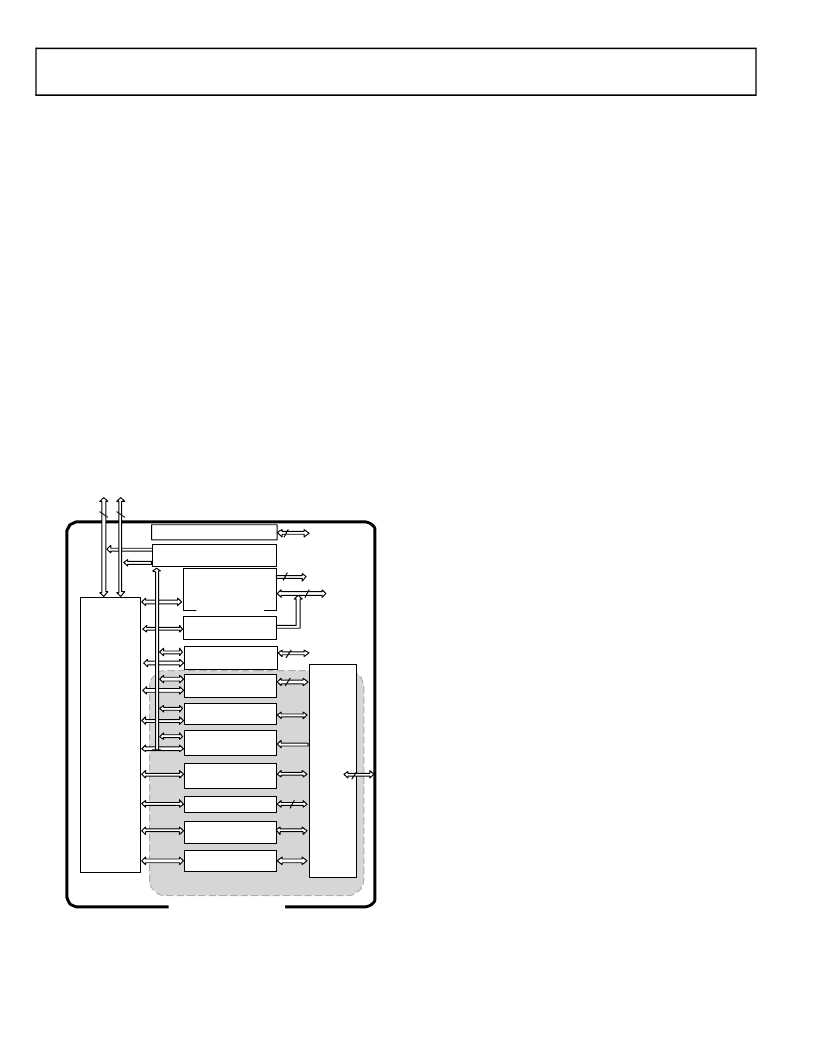

Digital Audio Interface (DAI)

The Digital Audio Interface (DAI) provides the ability to con-

nect various peripherals to any of the SHARCs DAI pins

(DAI_P20–1).

Programs make these connections using the Signal Routing

Unit (SRU, shown in

Figure 3

).

The SRU is a matrix routing unit (or group of multiplexers) that

enables the peripherals provided by the DAI to be intercon-

nected under software control. This allows easy use of the DAI

associated peripherals for a much wider variety of applications

by using a larger set of algorithms than is possible with noncon-

figurable signal paths.

The DAI also includes six serial ports, two precision clock gen-

erators (PCGs), eight channels of asynchronous sample rate

converters, an input data port (IDP), an SPI port, six flag out-

puts and six flag inputs, and three timers. The IDP provides an

additional input path to the ADSP-21364 core, configurable as

either eight channels of I

2

S serial data or as seven channels plus

a single 20-bit wide synchronous parallel data acquisition port.

Each data channel has its own DMA channel that is indepen-

dent from the ADSP-21364's serial ports.

For complete information on using the DAI, see the

ADSP-

2136x SHARC Processor Hardware Reference

.

Serial Ports

The ADSP-21364 features six synchronous serial ports that pro-

vide an inexpensive interface to a wide variety of digital and

mixed-signal peripheral devices such as Analog Devices’

AD183x family of audio codecs, ADCs, and DACs. The serial

ports are made up of two data lines, a clock and frame sync. The

data lines can be programmed to either transmit or receive and

each data line has a dedicated DMA channel.

Serial ports are enabled via 12 programmable and simultaneous

receive or transmit pins that support up to 24 transmit or 24

receive channels of audio data when all six SPORTS are enabled,

or six full duplex TDM streams of 128 channels per frame.

The serial ports operate at a maximum data rate of 50M bits/s.

Serial port data can be automatically transferred to and from

on-chip memory via dedicated DMA channels. Each of the

serial ports can work in conjunction with another serial port to

provide TDM support. One SPORT provides two transmit sig-

nals while the other SPORT provides the two receive signals.

The frame sync and clock are shared.

Serial ports operate in four modes:

Standard DSP serial mode

Multichannel (TDM) mode

I

2

S mode

Left-justified sample pair mode

Left-justified sample pair mode is a mode where in each frame

sync cycle two samples of data are transmitted/received—one

sample on the high segment of the frame sync, the other on the

low segment of the frame sync. Programs have control over var-

ious attributes of this mode.

Figure 3. ADSP-21364 I/O Processor and Peripherals Block Diagram

16

3

PRECISION CLOCK

GENERATORS (2)

SPI PORT (1)

4

SERIAL PORTS (6)

INPUT

DATA PORTS (8)

TIMERS (3)

3

DMA CONTROLLER

25 CHANNE LS

I

(

C

I/O PROCESSOR

PARALLEL PORT

4

GPIO FLAGS/IRQ/TIMEXP

S

ADDRE SS /DATA BUS/ GP IO

CONTROL/G PIO

DIGITAL AUDIO INTERFACE

TO PROCESSOR BUSSES AND

SYSTEM MEMORY

IO ADDRESS

BUS (18)

PWM (16)

IO DATA

BUS (32)

SPI PORT (1)

4

20

SRC (8 CHANNELS)

SPDIF (RX/TX)

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21364SBBC-ENG | SHARC Processor |

| ADSP-21364SBBCZENG | SHARC Processor |

| ADSP-21364SBSQ-ENG | SHARC Processor |

| ADSP-21364SBSQZENG | SHARC Processor |

| ADSP-21364SCSQ-ENG | SHARC Processor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-21364BBC-1AA | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| ADSP-21364BBC-1AAZ | 制造商:Analog Devices 功能描述:DSP 32BIT SHARC 333MHZ 136CSPBGA |

| ADSP-21364BBCZ-1AA | 功能描述:IC DSP 32BIT 333MHZ 136-CSPBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21364BSQZ-1AX | 制造商:Analog Devices 功能描述:333 MHZ, PROCESSOR W/ON CHIP ROM,S/PDIF - Trays |

| ADSP-21364BSWZ-1AA | 功能描述:IC DSP 32BIT 333MHZ EPAD 144LQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:40 系列:TMS320DM64x, DaVinci™ 類型:定點 接口:I²C,McASP,McBSP 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:160kB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:0°C ~ 90°C 安裝類型:表面貼裝 封裝/外殼:548-BBGA,FCBGA 供應商設備封裝:548-FCBGA(27x27) 包裝:托盤 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

發布緊急采購,3分鐘左右您將得到回復。