- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374033 > ADSP-21364SCSQ-ENG (ANALOG DEVICES INC) SHARC Processor PDF資料下載

參數(shù)資料

| 型號: | ADSP-21364SCSQ-ENG |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | SHARC Processor |

| 中文描述: | 16-BIT, 55.55 MHz, OTHER DSP, PQFP144 |

| 封裝: | MS-026BFB-HD, HSLQFP-144 |

| 文件頁數(shù): | 36/52頁 |

| 文件大小: | 853K |

| 代理商: | ADSP-21364SCSQ-ENG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Rev. PrB

|

Page 36 of 52

|

September 2004

ADSP-21364

Preliminary Technical Data

SPDIF Transmitter

Serial data input to the SPDIF transmitter can be formatted as

left justified, I

2

S or right justified with word widths of 16, 18, 20,

or 24 bits. The following sections provide timing for the

transmitter.

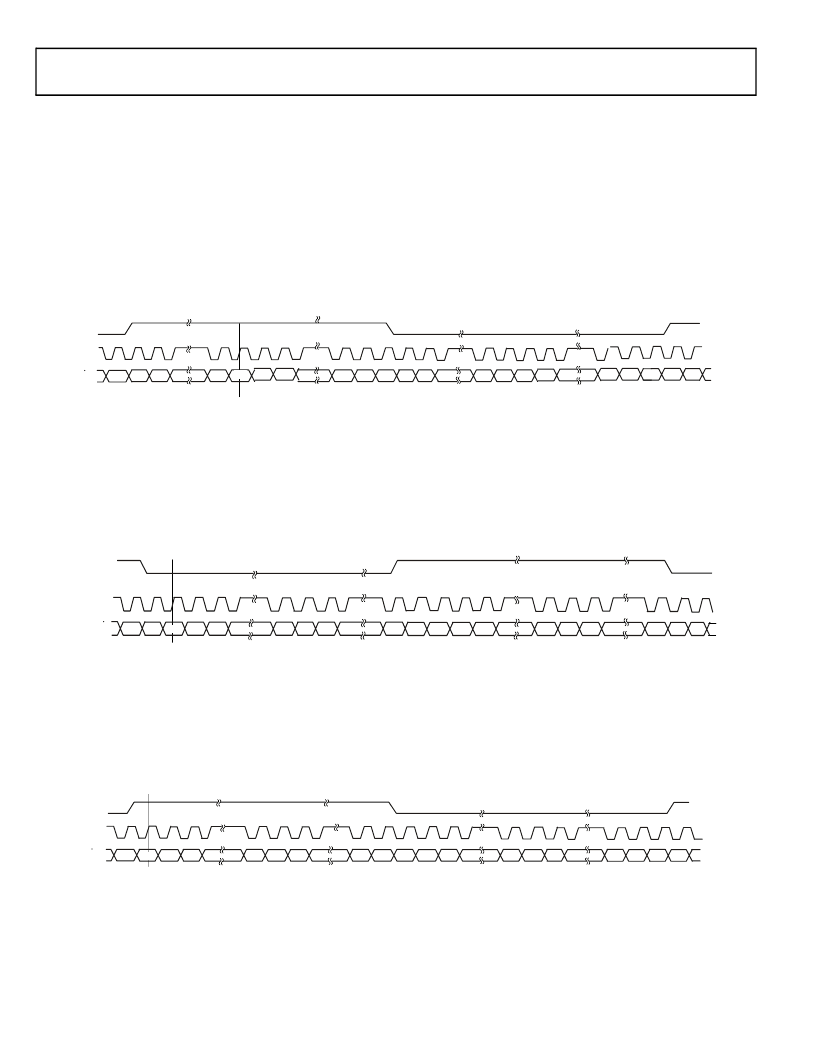

SPDIF Transmitter—Serial Input Waveforms

Figure 27

shows the right-justified mode. LRCLK is HI for the

left channel and LO for the right channel. Data is valid on the

rising edge of SCLK. The MSB is delayed 12-bit clock periods

(in 20-bit output mode) or 16-bit clock periods (in 16-bit output

mode) from an LRCLK transition, so that when there are 64

SCLK periods per LRCLK period, the LSB of the data will be

right-justified to the next LRCLK transition.

Figure 28

shows the default I2S-justified mode. LRCLK is LO

for the left channel and HI for the right channel. Data is valid on

the rising edge of SCLK. The MSB is left-justified to an LRCLK

transition but with a single SCLK period delay.

Figure 29

shows the left-justified mode. LRCLK is HI for the left

channel and LO for the right channel. Data is valid on the rising

edge of SCLK. The MSB is left-justified to an LRCLK transition

with no MSB delay.

Figure 27. Right-Justified Mode

LRCLK

SCLK

SDATA

LEFT CHANNEL

RIGHT CHANNEL

MSB-1

MSB-2

LSB+2 LSB+1

LSB

MSB

MSB-1

MSB-2

LSB+2

LSB+1

LSB

LSB

MSB

Figure 28. I

2

S-Justified Mode

MSB-1

MSB-2

LSB+2 LSB+1

LSB

LRCLK

SCLK

SDATA

LEFTCHANNEL

RIGHTCHANNEL

MSB

MSB-1

MSB-2

LSB+2

LSB+1

LSB

MSB

MSB

Figure 29. Left-Justified Mode

LRCLK

SCLK

SDATA

LEFT CHANNEL

RIGHT CHANNEL

MSB-1

MSB-2

LSB+2

LSB+1

LSB

MSB

MSB-1

MSB-2

LSB+2

LSB+1

LSB

MSB

MSB+1

MSB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-21364SCSQZENG | SHARC Processor |

| ADSP-21364SKBC-ENG | SHARC Processor |

| ADSP-21364SKBCZENG | SHARC Processor |

| ADSP-21364SKSQ-ENG | SHARC Processor |

| ADSP-21364SKSQZENG | SHARC Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-21364SCSQZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21364SKBC-ENG | 制造商:Analog Devices 功能描述: |

| ADSP-21364SKBCZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21364SKSQ-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21364SKSQZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。