- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄18702 > EFM32-TG222F32-SK (Energy Micro)IC MICRO KIT GECKO 48LQFP PDF資料下載

參數(shù)資料

| 型號(hào): | EFM32-TG222F32-SK |

| 廠商: | Energy Micro |

| 文件頁(yè)數(shù): | 60/136頁(yè) |

| 文件大小: | 0K |

| 描述: | IC MICRO KIT GECKO 48LQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Tiny Gecko |

| 套件類型: | 微控制器 |

| 值: | 2 件 - 閃存 - 32KB |

| 包裝: | 紙板盒 |

| 安裝類型: | 表面貼裝 |

| 包括封裝: | 48-LQFP |

| 其它名稱: | 914-1021 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)當(dāng)前第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)

...the world's most energy friendly microcontrollers

2011-02-04 - d0002_Rev1.00

3

www.energymicro.com

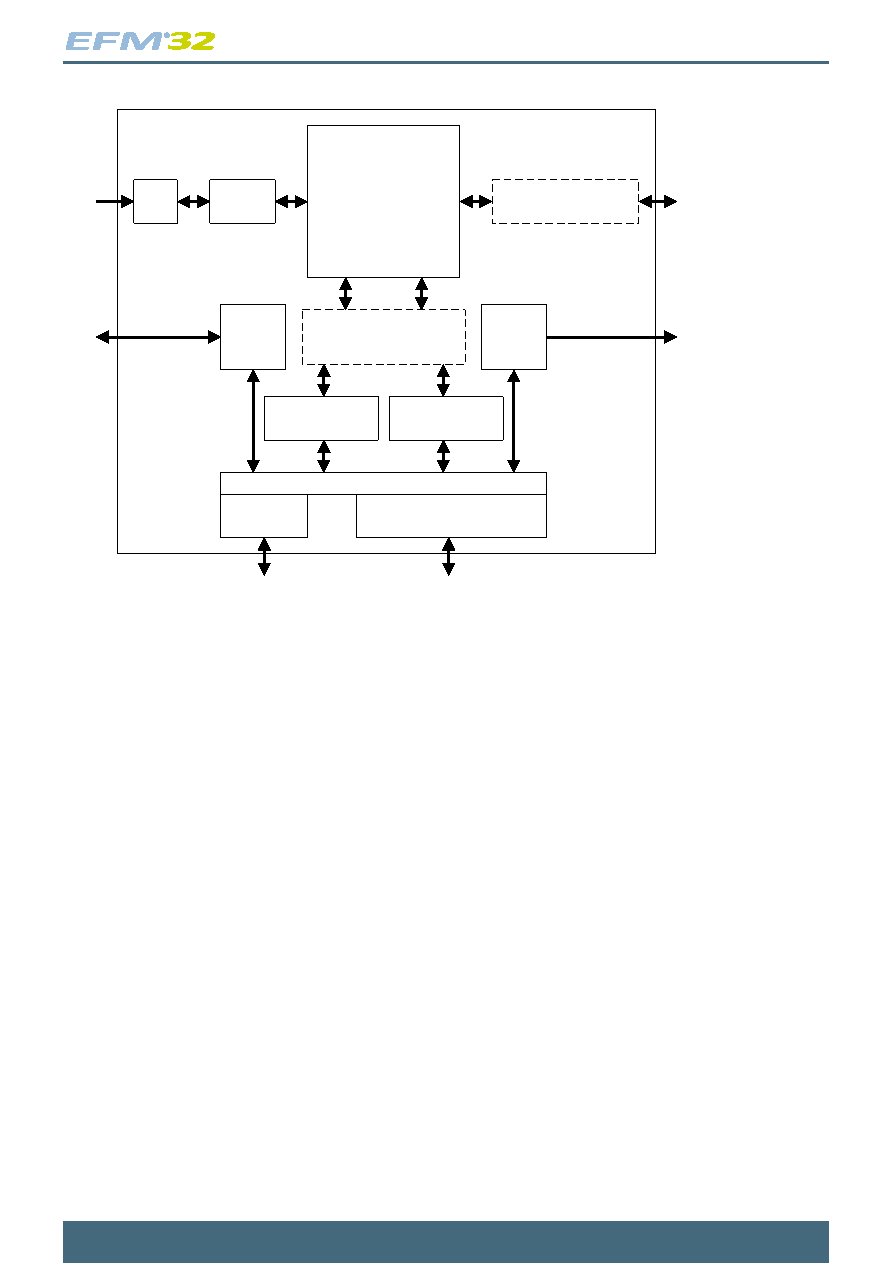

Figure 1.1. EFM32 Cortex-M3 implementation

Processor

core

NVIC

Debug

Access

Port

Mem ory

prot ect ion unit

WIC

Serial

Wire

viewer

Bus m at rix

Code

int erface

SRAM and

peripheral int erface

Dat a

wat chpoint s

Flash

pat ch

EFM32 Cort ex-M3

processor

Em bedded Trace

Macrocell

The Cortex-M3 processor is built on a high-performance processor core, with a 3-stage pipeline Harvard

architecture, making it ideal for demanding embedded applications. The processor delivers exceptional

power efficiency through an efficient instruction set and extensively optimized design, providing high-

end processing hardware including single-cycle 32x32 multiplication and dedicated hardware division.

To facilitate the design of cost-sensitive devices, the Cortex-M3 processor implements tightly-coupled

system components that reduce processor area while significantly improving interrupt handling and

system debug capabilities. The Cortex-M3 processor implements a version of the Thumb instruction

set, ensuring high code density and reduced program memory requirements. The Cortex-M3 instruction

set provides the exceptional performance expected of a modern 32-bit architecture, with the high code

density of 8-bit and 16-bit microcontrollers.

The Cortex-M3 processor closely integrates a configurable nested interrupt controller (NVIC), to deliver

industry-leading interrupt performance. The NVIC includes a non-maskable interrupt (NMI), and provides

up to 8 interrupt priority levels. The tight integration of the processor core and NVIC provides fast

execution of interrupt service routines (ISRs), dramatically reducing the interrupt latency. This is

achieved through the hardware stacking of registers, and the ability to suspend load-multiple and store-

multiple operations. Interrupt handlers do not require any assembler stubs, removing any code overhead

from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from

one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep

function that enables the entire device to be rapidly powered down.

1.2.1 System level interface

The Cortex-M3 processor provides multiple interfaces using AMBA technology to provide high

speed, low latency memory accesses. It supports unaligned data accesses and implements atomic bit

manipulation that enables faster peripheral controls, system spinlocks and thread-safe Boolean data

handling.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EFM32-TG230F32-SK | IC MICRO KIT GECKO 64QFN |

| EFM32-TG210F32-SK | IC MICRO KIT GECKO 32QFN |

| 1267 X 6" | TAPE ALUMINUM FOIL 6" X 1FT |

| 7810 0.25MM | ECAP COND PAD .25MM 7.7" X 10" |

| 7810 0.20MM | ECAP COND PAD .20MM 7.7" X 10" |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EFM32TG222F32-T | 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 32KB FLASH 48TQFP |

| EFM32TG222F8 | 功能描述:ARM微控制器 - MCU 8KB Flash 2KB RAM RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 處理器系列:STM32F373xx 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:72 MHz 程序存儲(chǔ)器大小:256 KB 數(shù)據(jù) RAM 大小:32 KB 片上 ADC:Yes 工作電源電壓:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:LQFP-48 安裝風(fēng)格:SMD/SMT |

| EFM32TG222F8-QFP48 | 制造商:Energy Micro AS 功能描述:TINY GECKO MCU - Tape and Reel 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 8KB FLASH 48TQFP |

| EFM32TG222F8-QFP48T | 制造商:Energy Micro AS 功能描述:32 BIT ARM MPU, TINY GECKO - Trays |

| EFM32TG222F8-QFP48-T | 制造商:Energy Micro AS 功能描述:IC MCU 32BIT 8KB FLASH 48TQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。