- 您現在的位置:買賣IC網 > PDF目錄385400 > HT48RB8 (Holtek Semiconductor Inc.) 8-Bit USB Type OTP MCU PDF資料下載

參數資料

| 型號: | HT48RB8 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit USB Type OTP MCU |

| 中文描述: | 8位微控制器的USB型檢察官辦公室 |

| 文件頁數: | 13/45頁 |

| 文件大小: | 281K |

| 代理商: | HT48RB8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

HT48RB8

Rev. 1.30

13

February 10, 2003

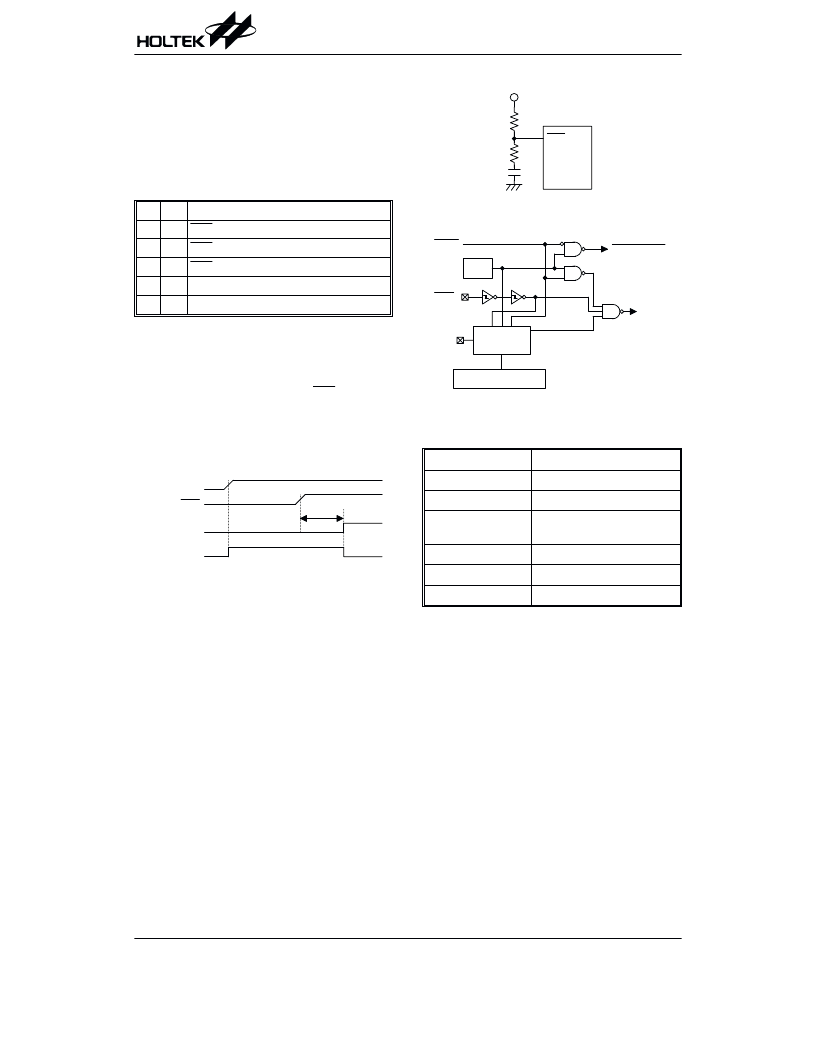

The WDT time-out during HALT is different from other

chip reset conditions, since it can perform a warm re -

set thatresetsonlythePCandSP,leavingtheothercir-

cuits in their original state. Some registers remain un-

changed during other reset conditions. Most registers

are reset to the initial condition when the reset condi-

tions are met. By examining the PD and TO flags, the

programcandistinguishbetweendifferent chipresets .

TO

PD

RESET Conditions

0

0

RES reset during power-up

u

u

RES reset during normal operation

0

1

RES wake-up HALT

1

u

WDT time-out during normal operation

1

1

WDT wake-up HALT

Note: u stands for unchanged

To guarantee that the system oscillator is started and

stabilized, the SST (System Start-up Timer) provides an

extra-delay of 1024 system clock pulses when the sys-

tem reset (power-up, WDT time-out or RES reset) or the

system awakes from the HALT state.

When a system reset occurs, the SST delay is added

during the reset period. Any wake-up from HALT will en-

able the SST delay.

The functional unit chip reset status are shown below.

PC

000H

Interrupt

Disable

Prescaler

Clear

WDT

Clear. After master reset,

WDT begins counting

Timer/event Counter

Off

Input/output Ports

Input mode

SP

Points to the top of the stack

Reset circuit

+

(

!

+

2

#

, "

!

!

(

!

6

(

,

Reset configuration

(

6

$

( (

!

Reset timing chart

相關PDF資料 |

PDF描述 |

|---|---|

| HT49C10 | 8-BIT MICROCONTROLLER |

| HT49C30L | HDSP-A101 RED DISPLAY, LED, |

| HT49R30 | DISPLAY 7 SEGMENT |

| HT49R30A-1 | DISPL 7 SEG YELLOW |

| HT49C30-1 | 8-Bit LCD Type MCU |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HT48RU80 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:I/O Type 8-Bit MCU |

| HT48RXX | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit Microcontroller Series |

| HT-49 | 制造商:FCI 功能描述: |

| HT49010576-5 | 制造商:Rennsteig 功能描述:HVT 1.2 TERMINALS 22-18GA |

| HT49010577-5 | 制造商:Rennsteig 功能描述:HVT 1.2 TERMINALS 18-16GA |

發布緊急采購,3分鐘左右您將得到回復。