- 您現在的位置:買賣IC網 > PDF目錄361030 > LM5642 (National Semiconductor Corporation) High Voltage, Dual Synchronous Buck Converter with Oscillator Synchronization PDF資料下載

參數資料

| 型號: | LM5642 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | High Voltage, Dual Synchronous Buck Converter with Oscillator Synchronization |

| 中文描述: | 高電壓,雙同步降壓轉換器振蕩器同步 |

| 文件頁數: | 20/24頁 |

| 文件大小: | 667K |

| 代理商: | LM5642 |

Input Capacitor Selection

(Continued)

3.

Both duty cycles are greater than D

MAX

. This case is

identical to a system at 200kHz where either duty cycle

is 50% or greater. Some overlap of duty cycles is guar-

anteed, and hence the second, more complicated rms

input current equation must be used.

Input capacitors must meet the minimum requirements of

voltage and ripple current capacity. The size of the capacitor

should then be selected based on hold up time require-

ments. Bench testing for individual applications is still the

best way to determine a reliable input capacitor value. Input

capacitors should always be placed as close as possible to

the current sense resistor or the drain of the top FET. When

high ESR capacitors such as tantalum are used, a 1μF

ceramic capacitor should be added as closely as possible to

the high-side FET drain and low-side FET source.

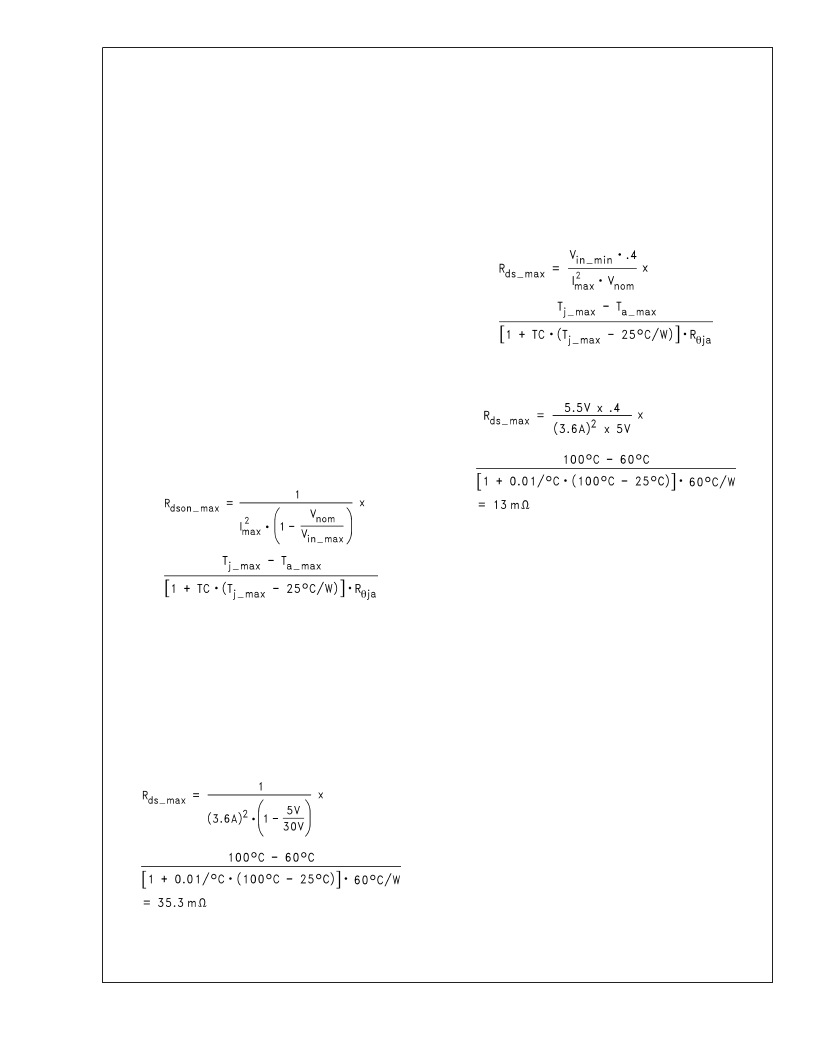

MOSFET Selection

BOTTOM FET SELECTION

During normal operation, the bottom FET is switching on and

off at almost zero voltage. Therefore, only conduction losses

are present in the bottom FET. The most important param-

eter when selecting the bottom FET is the on resistance

(R

DS-ON

). The lower the on resistance, the lower the power

loss. The bottom FET power loss peaks at maximum input

voltage and load current. The equation for the maximum

allowed on resistance at room temperature for a given FET

package, is:

(25)

where Tj_max is the maximum allowed junction temperature

in the FET, Ta_max is the maximum ambient temperature,

R

θ

ja

is the junction-to-ambient thermal resistance of the FET,

and TC is the temperature coefficient of the on resistance

which is typically in the range of 10,000ppm/C.

If the calculated R

DS-ON (MAX)

is smaller than the lowest

value available, multiple FETs can be used in parallel. This

effectively reduces the Imax term in the above equation, thus

reducing R

. When using two FETs in parallel, multiply

the calculated R

by 4 to obtain the R

for each FET. In the case of three FETs, multiply by 9.

(26)

If the selected FET has an Rds value higher than 35.3

,

then two FETs with an R

DS-ON

less than 141m

(4 x

35.3m

) can be used in parallel. In this case, the tempera-

ture rise on each FET will not go to Tj_max because each

FET is now dissipating only half of the total power.

TOP FET SELECTION

The top FET has two types of losses: switching loss and

conduction loss. The switching losses mainly consist of

crossover loss and bottom diode reverse recovery loss.

Since it is rather difficult to estimate the switching loss, a

general starting point is to allot 60% of the top FET thermal

capacity to switching losses. The best way to precisely de-

termine switching losses is through bench testing. The equa-

tion for calculating the on resistance of the top FET is thus:

(27)

Example: Tj_max = 100C, Ta_max = 60C, Rqja = 60C/W,

Vin_min = 5.5V, Vnom = 5V, and Iload_max = 3.6A.

(28)

When using FETs in parallel, the same guidelines apply to

the top FET as apply to the bottom FET.

Loop Compensation

The general purpose of loop compensation is to meet static

and dynamic performance requirements while maintaining

stability. Loop gain is what is usually checked to determine

small-signal performance. Loop gain is equal to the product

of control-output transfer function and the output-control

transfer function (the compensation network transfer func-

tion). Generally speaking it is a good idea to have a loop gain

slope that is -20dB /decade from a very low frequency to well

beyond the crossover frequency. The crossover frequency

should not exceed one-fifth of the switching frequency. The

higher the bandwidth is, the faster the load transient re-

sponse speed will potentially be. However, if the duty cycle

saturates during a load transient, further increasing the small

signal bandwidth will not help. Since the control-output trans-

fer function usually has very limited low frequency gain, it is

a good idea to place a pole in the compensation at zero

frequency, so that the low frequency gain will be relatively

large. A large DC gain means high DC regulation accuracy

(i.e. DC voltage changes little with load or line variations).

The rest of the compensation scheme depends highly on the

shape of the control-output plot.

L

www.national.com

20

相關PDF資料 |

PDF描述 |

|---|---|

| LM5642MTC | High Voltage, Dual Synchronous Buck Converter with Oscillator Synchronization |

| LM565 | Phase Locked Loop |

| LM565C | |

| LM565CH | Analog Phase-Locked Loop |

| LM565CN | Phase Locked Loop |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LM5642_07 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:High Voltage, Dual Synchronous Buck Converter with Oscillator Synchronization |

| LM5642EVAL-KIT | 功能描述:BOARD EVALUATION LM5642 RoHS:否 類別:編程器,開發系統 >> 評估板 - DC/DC 與 AC/DC(離線)SMPS 系列:PowerWise® 產品培訓模塊:Obsolescence Mitigation Program 標準包裝:1 系列:True Shutdown™ 主要目的:DC/DC,步升 輸出及類型:1,非隔離 功率 - 輸出:- 輸出電壓:- 電流 - 輸出:1A 輸入電壓:2.5 V ~ 5.5 V 穩壓器拓撲結構:升壓 頻率 - 開關:3MHz 板類型:完全填充 已供物品:板 已用 IC / 零件:MAX8969 |

| LM5642EVAL-KIT/NOPB | 功能描述:電源管理IC開發工具 LM5642 EVAL KIT RoHS:否 制造商:Maxim Integrated 產品:Evaluation Kits 類型:Battery Management 工具用于評估:MAX17710GB 輸入電壓: 輸出電壓:1.8 V |

| LM5642MH | 制造商:Texas Instruments 功能描述: |

| LM5642MH/NOPB | 功能描述:DC/DC 開關控制器 RoHS:否 制造商:Texas Instruments 輸入電壓:6 V to 100 V 開關頻率: 輸出電壓:1.215 V to 80 V 輸出電流:3.5 A 輸出端數量:1 最大工作溫度:+ 125 C 安裝風格: 封裝 / 箱體:CPAK |

發布緊急采購,3分鐘左右您將得到回復。