- 您現在的位置:買賣IC網 > PDF目錄361238 > Q67120-C508 IC-SM-8-BIT CPU 12-MHZ PDF資料下載

參數資料

| 型號: | Q67120-C508 |

| 英文描述: | IC-SM-8-BIT CPU 12-MHZ |

| 中文描述: | 集成電路釤8位CPU的12兆赫 |

| 文件頁數: | 87/121頁 |

| 文件大小: | 1000K |

| 代理商: | Q67120-C508 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁當前第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁

Interrupt System

C501

Semiconductor Group

7-9

Note that if an interrupt of a higher priority level goes active prior to S5P2 in the machine cycle

labeled C3 in

figure 7-26

then, in accordance with the above rules, it will be vectored to during C5

and C6 without any instruction for the lower priority routine to be executed.

Thus, the processor acknowledges an interrupt request by executing a hardware-generated LCALL

to the appropriate servicing routine. In some cases it also clears the flag that generated the

interrupt, while in other cases it does not; then this has to be done by the user’s software. The

hardware clears the external interrupt flags IE0 and IE1 only if they were transition-activated. The

hardware-generated LCALL pushes the contents of the program counter onto the stack (but it does

not save the PSW) and reloads the program counter with an address that depends on the source of

the interrupt being vectored too, as shown in the following

table 7-9

.

Execution proceeds from that location until the RETI instruction is encountered. The RETI

instruction informs the processor that the interrupt routine is no longer in progress, then pops the

two top bytes from the stack and reloads the program counter. Execution of the interrupted program

continues from the point where it was stopped. Note that the RETI instruction is very important

because it informs the processor that the program left the current interrupt priority level. A simple

RET instruction would also have returned execution to the interrupted program, but it would have

left the interrupt control system thinking an interrupt was still in progress. In this case no interrupt of

the same or lower priority level would be acknowledged.

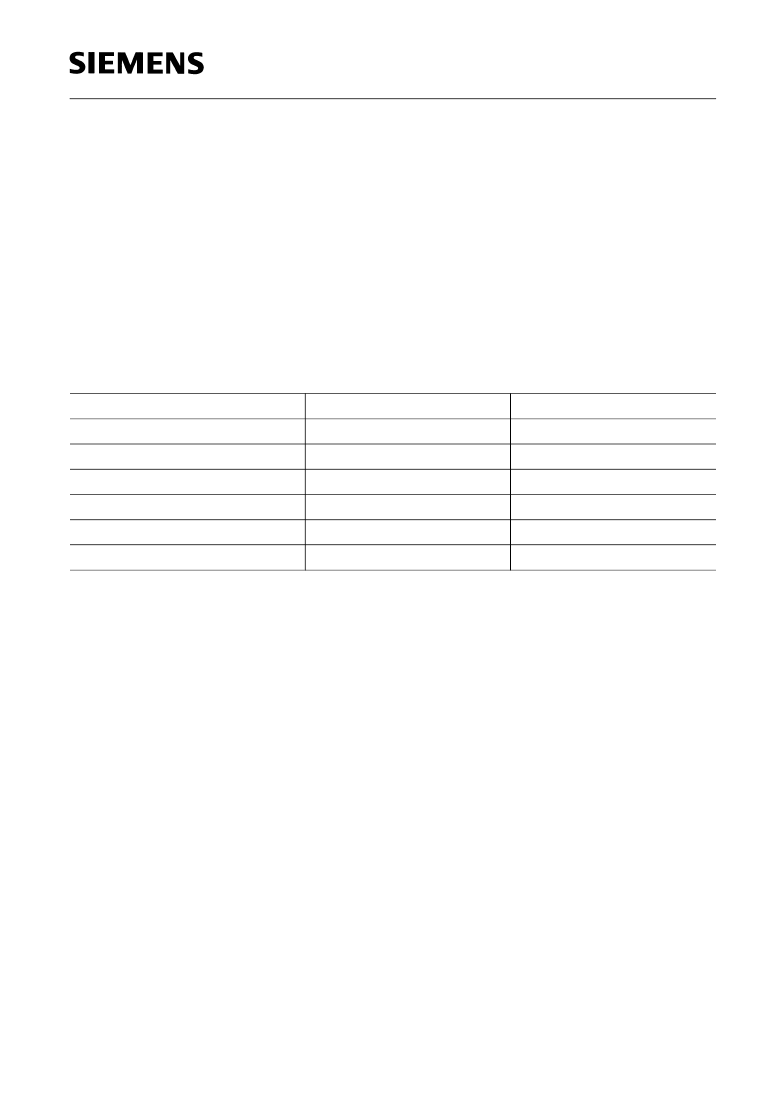

Table 7-9

Interrupt Source and Vectors

Interrupt Source

Interrupt Vector Address

Interrupt Request Flags

External Interrupt 0

0003H

000BH

0013H

001BH

0023H

002BH

IE0

Timer 0 Overflow

TF0

External Interrupt 1

IE1

Timer 1 Overflow

TF1

Serial Channel

RI / TI

Timer 2 Overflow / Ext. Reload

TF2 / EXF2

相關PDF資料 |

PDF描述 |

|---|---|

| Q67121C2168A1 | IC-SM-16 BIT CPU |

| Q67121C452 | IC-SM-8-BIT CPU-12MHZ |

| Q67126-C2088 | RF inductor, ceramic core, 2% tol, SMT, RoHS |

| Q67127-C2036SAB-C161R1-L16M | IC-SM-16 BIT CPU |

| Q67120-C2200 | 16-Bit Single-Chip Microcontroller Bare Die Delivery |

相關代理商/技術參數 |

參數描述 |

|---|---|

| Q67120-C517 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:HIGH PERFORMANCE 32-BIT RISC MICROPROCESSOR |

| Q67120-C552 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:HIGH-PERFORMANCE 16-BIT CMOS SINGLE-CHIP MICROCONTROLLERS FOR EMBEDDED CONTROL APPLICATIONS |

| Q67120-C556 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:WRITE BUFFER |

| Q67120-C557 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:WRITE BUFFER |

| Q67120-C582 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:8-Bit CMOS Single-Chip Microcontroller |

發布緊急采購,3分鐘左右您將得到回復。