- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382648 > TMX320F2810PBKAEP (Texas Instruments, Inc.) Digital Signal Processors PDF資料下載

參數(shù)資料

| 型號: | TMX320F2810PBKAEP |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | Digital Signal Processors |

| 中文描述: | 數(shù)字信號處理器 |

| 文件頁數(shù): | 52/103頁 |

| 文件大小: | 1341K |

| 代理商: | TMX320F2810PBKAEP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當前第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁

TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B

–

APRIL 2001

–

REVISED SEPTEMBER 2001

52

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251

–

1443

watchdog block (continued)

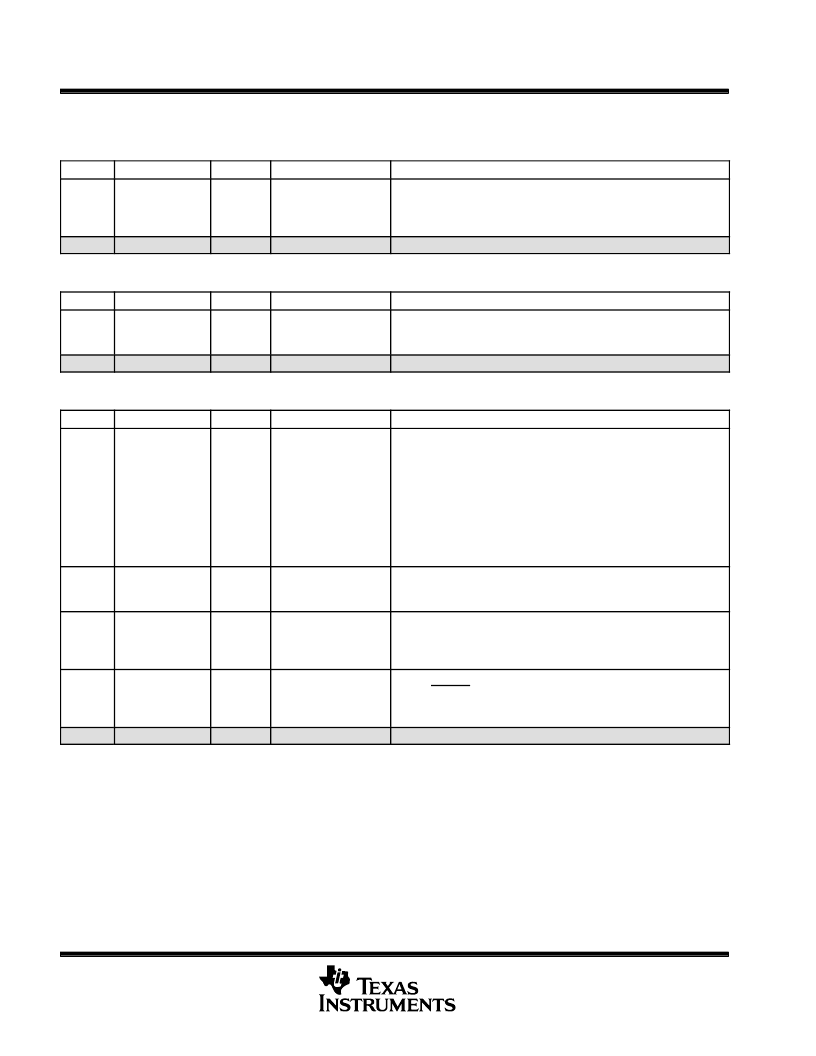

Table 37. WDCNTR Register Bit Definitions

BIT(S)

NAME

TYPE

RESET

DESCRIPTION

7:0

WDCNTR

R/W

0:0

These bits contain the current value of the WD counter. The 8-bit

counter continually increments at the WDCLK rate. If the counter

overflows, then the watchdog initiates a reset. If the WDKEY register

is written with a valid combination, then the counter is reset to zero.

15:8

reserved

R=0

0:0

Table 38. WDKEY Register Bit Definitions

BIT(S)

NAME

TYPE

RESET

DESCRIPTION

7:0

WDKEY

W/R=0

0:0

Writing 0x55 followed by 0xAA will cause the WDCNTR bits to be

cleared. Writing any other value will cause an immediate watchdog

reset to be generated.

15:8

reserved

R=0

0:0

Table 39. WDCR Register Bit Definitions

BIT(S)

NAME

TYPE

RESET

DESCRIPTION

2:0

WDPS(2:0)

R/W

0:0

These bits configure the watchdog counter clock (WDCLK) rate relative

to OSCCLK/512:

000

WDCLK = OSCCLK/512/1

001

WDCLK = OSCCLK/512/1

010

WDCLK = OSCCLK/512/2

011

WDCLK = OSCCLK/512/4

100

WDCLK = OSCCLK/512/8

101

WDCLK = OSCCLK/512/16

110

WDCLK = OSCCLK/512/32

111

WDCLK = OSCCLK/512/64

5:3

WDCHK(2:0)

W/R=0

0:0

The user must ALWAYS write

“

1,0,1

”

to these bits whenever a write to

this register is performed. Writing any other value will cause an

immediate reset to the core (if WD enabled).

6

WDDIS

R/W

0

Writing a 1 to this bit will disable the watchdog module. Writing a 0 will

enable the module. This bit can only be modified if the WDOVERRIDE

bit in the SCSR2 register is set to 1. On reset, the watchdog module is

enabled.

7

WDFLAG

R/W=1

Watchdog reset status flag bit. This bit, if set, indicates a watchdog

reset (WDRST) generated the reset condition. If 0, then it was an

external device or power-up reset condition. This bit remains latched

until the user writes a 1 to clear the condition. Writes of 0 will be ignored.

15:8

reserved

R=0

0:0

P

相關PDF資料 |

PDF描述 |

|---|---|

| TMP320F2810PBKAEP | Digital Signal Processors |

| TMX320F2810PBKS | DIGITAL SIGNAL PROCESSORS |

| TMP320F2810PBKS | DIGITAL SIGNAL PROCESSORS |

| TMP320F2810GHHA | DIGITAL SIGNAL PROCESSORS |

| TMX320F2810GHHMEP | Digital Signal Processors |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TMX320F2810PBKS | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSORS |

| TMX320F2810PGFA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSORS |

| TMX320F2810PGFAEP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Signal Processors |

| TMX320F2810PGFS | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSORS |

| TMX320F2811GHHA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

發(fā)布緊急采購,3分鐘左右您將得到回復。