- 您現在的位置:買賣IC網 > PDF目錄382721 > UDA1380 Stereo audio coder-decoder for MD, CD and MP3 PDF資料下載

參數資料

| 型號: | UDA1380 |

| 英文描述: | Stereo audio coder-decoder for MD, CD and MP3 |

| 中文描述: | 立體聲音頻編碼器,可用于MD,CD和MP3解碼器 |

| 文件頁數: | 19/68頁 |

| 文件大小: | 278K |

| 代理商: | UDA1380 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

2002 Sep 16

19

Philips Semiconductors

Product specification

Stereo audio coder-decoder

for MD, CD and MP3

UDA1380

8.11.1

A

NALOG FRONT

-

END

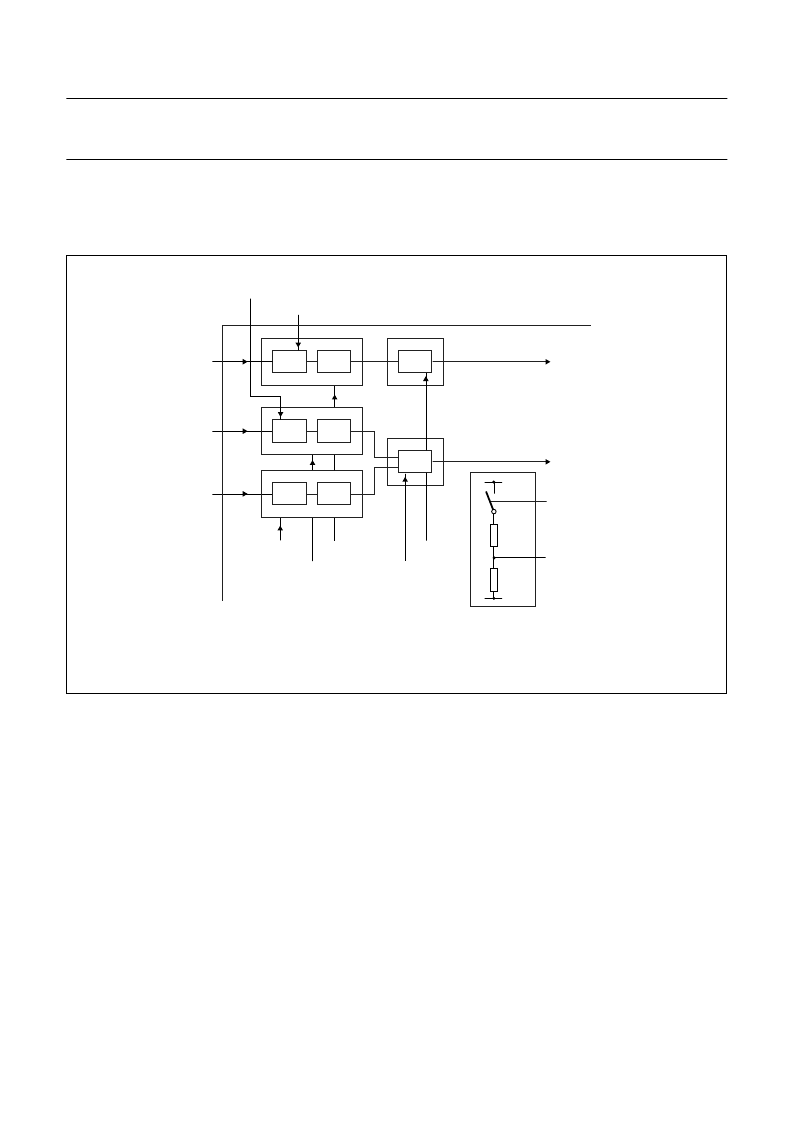

Figure 12 shows the power control inside the analog front-end. The control of all power-on pins of the ADC front-end is

done via separate L3-bus or I

2

C-bus bits.

handbook, full pagewidth

PGA

PGA_GAINCTRLR

PGA_GAINCTRLL

ADC

bitstream

right

ADC

SDC

bitstream

left

MGU534

PGA

VINL

VINR

VINM

SDC

LNA

SDC

PON_PGAL

PON_ADCL

PON_BIAS

FE

BIAS

VREF

PON_PGAR

PON_ADCR

PON_LNA

31

(27)

(29)

(31)

1

3

Fig.12 Analog front-end power-down.

Pin numbers for UDA1380HN in parentheses.

8.11.2

FSDAC

POWER CONTROL

The FSDAC block has power-on pins: one of which shuts

down the DAC itself, but leaves the output still at V

REF

voltage (which is half the power supply). This function is

set by the bit PON_DAC in the L3-bus or I

2

C-bus register.

A second L3-bus or I

2

C-bus bit shuts down the complete

bias circuit of the FSDAC, via bit PON_BIAS in the

L3-bus or I

2

C-bus register. This bit PON_BIAS acts the

same as given in Fig.12 for the analog front-end.

8.12

Plop prevention

Plops are ticks and other strange sounds, that can occur

when a part of a device is powered-up or powered-down,

or when switching between modes is done.

Some ways to prevent plops from occurring are:

When the FSDAC or headphone driver must be

powered-down, first a digital mute is applied. After that

the FSDAC or headphone driver can be powered-down.

In case the FSDAC or headphone driver must be

powered-up,firsttheanalogpartisswitchedon,thenthe

digital part is demuted

When the ADC must be powered-down, a digital mute

sequence must be applied. When the digital output

signal is completely muted, the ADC can be

powered-down. In case the ADC must be powered-up,

firsttheanalogpart mustbepowered-up, thenthedigital

part must be demuted

When there is a change of for example clock divider

settings or clock source (selecting between SYSCLK

and WSPLL clock), then also digital mute for that block

(either decimator or interpolator) should be used.

Remark

: All items mentioned in Section 8.12 are not

‘hard-wired’ implemented, but to be followed by the users

as a guideline for plop prevention.

相關PDF資料 |

PDF描述 |

|---|---|

| UDA1380TT | Stereo audio coder-decoder for MD, CD and MP3 |

| UDA1384 | Multichannel audio coder-decoder |

| UDA1384H | Multichannel audio coder-decoder |

| UDN2878W-2 | 10A SCRS |

| UDZ2.4B | Low Current Operation at 250 ,Low Reverse Leakage,Low Noise Zener Diode |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UDA1380HN | 制造商:ICS 制造商全稱:ICS 功能描述:Stereo audio coder-decoder for MD, CD and MP3 |

| UDA1380HN/N2 | 制造商:NXP Semiconductors 功能描述:IC CODEC AUDIO MINIDISC 32HVQFN 制造商:NXP Semiconductors 功能描述:IC, CODEC, AUDIO, MINIDISC, 32HVQFN |

| UDA1380HN/N2,118 | 功能描述:接口—CODEC STEREO AUDIO RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| UDA1380HN-T | 功能描述:接口—CODEC STEREO AUDIO CODER-DECODER RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| UDA1380TT | 功能描述:接口—CODEC SSA CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。