- 您現在的位置:買賣IC網 > PDF目錄382721 > UDA1380 Stereo audio coder-decoder for MD, CD and MP3 PDF資料下載

參數資料

| 型號: | UDA1380 |

| 英文描述: | Stereo audio coder-decoder for MD, CD and MP3 |

| 中文描述: | 立體聲音頻編碼器,可用于MD,CD和MP3解碼器 |

| 文件頁數: | 30/68頁 |

| 文件大小: | 278K |

| 代理商: | UDA1380 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

2002 Sep 16

30

Philips Semiconductors

Product specification

Stereo audio coder-decoder

for MD, CD and MP3

UDA1380

11.1

Evaluation modes and clock settings

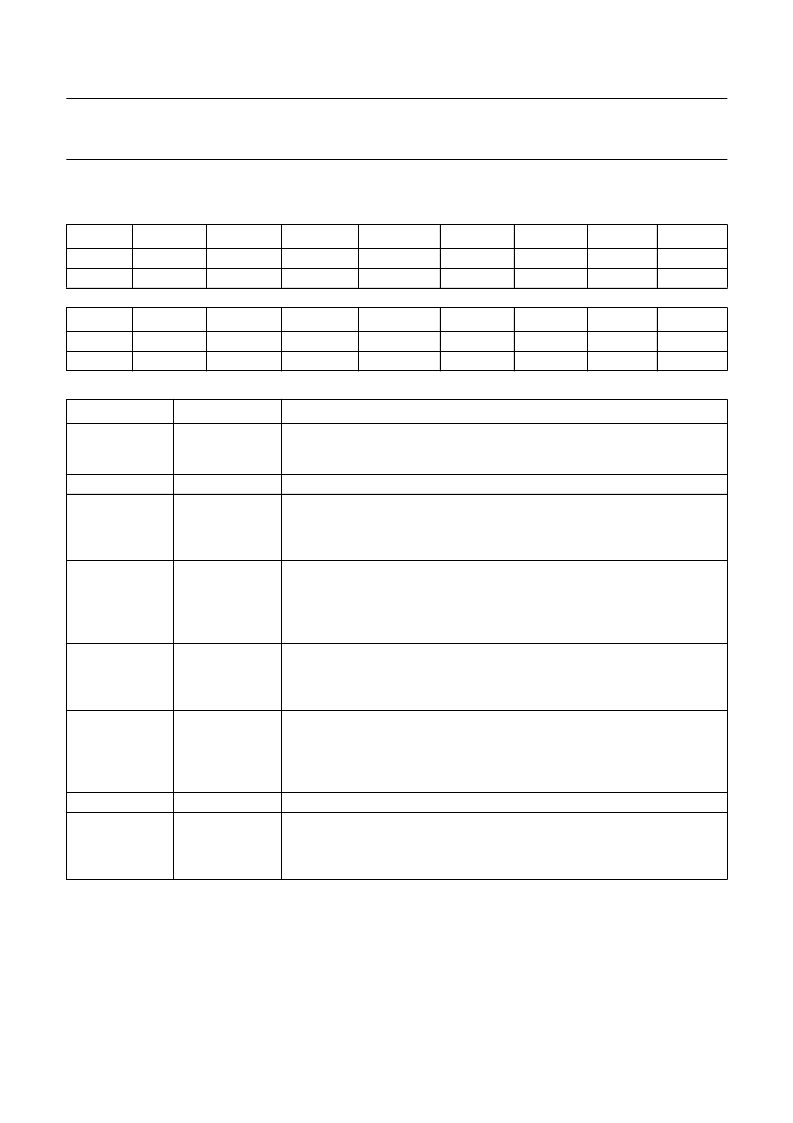

Table 17

Register address 00H

Table 18

Description of register bits

BIT

15

14

13

12

0

11

10

9

8

Symbol

Default

EV2

0

EV1

0

EV0

0

EN_ADC

0

EN_DEC

1

EN_DAC

0

EN_INT

1

BIT

7

0

6

0

5

4

3

2

1

0

Symbol

Default

ADC_CLK

0

DAC_CLK

0

sys_div1

0

sys_div0

0

PLL1

1

PLL0

0

BIT

SYMBOL

DESCRIPTION

15 to 13

EV[2:0]

Evaluation bits.

Bits EV2, EV1 and EV0 are special control bits for

manufacturer’s evaluation and must always be kept at their default values for

normal operation of UDA1380; default value 000, see Table 17.

default value 0

ADC clock enable.

A 1-bit value to enable the system clock (from SYSCLK

input) to the analog part of the ADC. See Fig.5 for more detailed information.

When this bit is logic 0: clock to ADC disabled and when this bit is logic 1: clock

to ADC running. Default value 0.

Decimator clock enable.

A 1-bit value to enable the 128f

s

clock to the

decimator, the 128f

s

part of the I

2

S-bus output block and the clock to the ADC

L3-bus or I

2

C-bus registers. See Fig.5 for more detailed information. When this

bit is logic 0: clock to the decimator disabled. When this bit is logic 1: clock to

the decimator running. Default value 1.

FSDAC clock enable.

A 1-bit value to enable the 256f

s

clock to the analog part

of the FSDAC. See Fig.5 for more detailed information. When this bit is logic 0:

clock to FSDAC disabled. When this bit is logic 1: clock to the FSDAC running.

Default value 0.

Interpolator clock enable.

A 1-bit value to enable the 128f

s

clock to the

interpolator, the 128f

s

part of the I

2

S-bus input block and the interpolator

registers of the L3-bus or I

2

C-bus interface. See Fig.5 for more detailed

information. When this bit is logic 0: clock to the interpolator disabled. When

this bit is logic 1: clock to the interpolator running. Default value 1.

default value 00

ADC clock select.

A 1-bit value to select the 128f

s

clock and the clock of the

analog part for the decimator and the ADC. This can either be the clock derived

from the SYSCLK input or from the WSPLL. When this bit is logic 0: SYSCLK

is used. When this bit is logic 1: WSPLL is used. Default value 0.

12

11

EN_ADC

10

EN_DEC

9

EN_DAC

8

EN_INT

7 and 6

5

ADC_CLK

相關PDF資料 |

PDF描述 |

|---|---|

| UDA1380TT | Stereo audio coder-decoder for MD, CD and MP3 |

| UDA1384 | Multichannel audio coder-decoder |

| UDA1384H | Multichannel audio coder-decoder |

| UDN2878W-2 | 10A SCRS |

| UDZ2.4B | Low Current Operation at 250 ,Low Reverse Leakage,Low Noise Zener Diode |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UDA1380HN | 制造商:ICS 制造商全稱:ICS 功能描述:Stereo audio coder-decoder for MD, CD and MP3 |

| UDA1380HN/N2 | 制造商:NXP Semiconductors 功能描述:IC CODEC AUDIO MINIDISC 32HVQFN 制造商:NXP Semiconductors 功能描述:IC, CODEC, AUDIO, MINIDISC, 32HVQFN |

| UDA1380HN/N2,118 | 功能描述:接口—CODEC STEREO AUDIO RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| UDA1380HN-T | 功能描述:接口—CODEC STEREO AUDIO CODER-DECODER RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| UDA1380TT | 功能描述:接口—CODEC SSA CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。