- 您現在的位置:買賣IC網 > PDF目錄250212 > 70V659S10DR (INTEGRATED DEVICE TECHNOLOGY INC) 128K X 36 DUAL-PORT SRAM, 10 ns, PQFP208 PDF資料下載

參數資料

| 型號: | 70V659S10DR |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 128K X 36 DUAL-PORT SRAM, 10 ns, PQFP208 |

| 封裝: | 28 X 28 MM, 3.50 MM HEIGHT, PLASTIC, QFP-208 |

| 文件頁數: | 13/24頁 |

| 文件大小: | 316K |

| 代理商: | 70V659S10DR |

IDT70V659/58/57S

High-Speed 3.3V 128/64/32K x 36 Asynchronous Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

20

Busy Logic

BusyLogicprovidesahardwareindicationthatbothportsoftheRAM

haveaccessedthesamelocationatthesametime.Italsoallowsoneofthe

twoaccessestoproceedandsignalstheothersidethattheRAMis“Busy”.

TheBUSYpincanthenbeusedtostalltheaccessuntiltheoperationon

theothersideiscompleted.Ifawriteoperationhasbeenattemptedfrom

thesidethatreceivesaBUSYindication,thewritesignalisgatedinternally

to prevent the write from proceeding.

TheuseofBUSYlogicisnotrequiredordesirableforallapplications.

InsomecasesitmaybeusefultologicallyORtheBUSYoutputstogether

and use any BUSY indication as an interrupt source to flag the event of

anillegalorillogicaloperation.IfthewriteinhibitfunctionofBUSYlogicis

notdesirable,theBUSYlogiccanbedisabledbyplacingthepartinslave

modewiththeM/Spin.OnceinslavemodetheBUSYpinoperatessolely

asawriteinhibitinputpin.Normaloperationcanbeprogrammedbytying

the BUSY pins HIGH. If desired, unintended write operations can be

prevented to a port by tying the BUSY pin for that port LOW.

The BUSY outputs on the IDT70V659/58/57 RAM in master mode,

arepush-pulltypeoutputsanddonotrequirepullupresistorstooperate.

If these RAMs are being expanded in depth, then the BUSY indication

for the resulting array requires the use of an external AND gate.

Iftwoormoremasterpartswereusedwhenexpandinginwidth,asplit

decisioncouldresultwithonemasterindicatingBUSYononesideofthe

array and another master indicating BUSY on one other side of

thearray.Thiswouldinhibitthewriteoperationsfromoneportforpartof

awordandinhibitthewriteoperationsfromtheotherportforthe otherpart

of the word.

The BUSY arbitration on a master is based on the chip enable and

address signals only. It ignores whether an access is a read or write. In

a master/slave array, both address and chip enable must be valid long

enoughforaBUSYflagtobeoutputfromthemasterbeforethe actualwrite

pulsecanbeinitiatedwiththeR/W signal.Failureto observethistiming

canresultinaglitchedinternalwriteinhibitsignalandcorrupteddatainthe

slave.

Semaphores

The IDT70V659/58/57 is an extremely fast Dual-Port 128/64/32K x

36CMOSStaticRAMwithanadditional8addresslocationsdedicatedto

binarysemaphoreflags.Theseflagsalloweitherprocessorontheleftor

right sideoftheDual-PortRAMtoclaimaprivilegeovertheotherprocessor

forfunctionsdefinedbythesystemdesigner’ssoftware.Asanexample,

the semaphore can be used by one processor to inhibit the other from

accessingaportionoftheDual-PortRAMoranyothersharedresource.

TheDual-PortRAMfeaturesafastaccesstime,withbothportsbeing

completelyindependentofeachother.Thismeansthatthe activityonthe

left port in no way slows the access time of the right port. Both ports are

identicalinfunctiontostandardCMOSStaticRAMandcanbereadfrom

orwrittentoatthesametimewiththeonlypossibleconflictarisingfromthe

simultaneous writing of, or a simultaneous READ/WRITE of, a non-

semaphorelocation.Semaphoresareprotectedagainstsuchambiguous

situationsandmaybeusedbythesystemprogramtoavoidanyconflicts

inthenon-semaphoreportionoftheDual-PortRAM.Thesedeviceshave

anautomaticpower-downfeaturecontrolledbyCE,theDual-PortRAM

enable,andSEM,thesemaphoreenable.TheCEandSEMpinscontrol

on-chip power down circuitry that permits the respective port to go into

standbymodewhennotselected.

SystemswhichcanbestusetheIDT70V659/58/57containmultiple

processors or controllers and are typically very high-speed systems

which are software controlled or software intensive. These systems

canbenefitfromaperformanceincreaseofferedbytheIDT70V659/58/

57shardwaresemaphores,whichprovidealockoutmechanismwithout

requiringcomplexprogramming.

Software handshaking between processors offers the maximum in

systemflexibilitybypermittingsharedresourcestobeallocatedinvarying

configurations. The IDT70V659/58/57 does not use its semaphore

flagstocontrolanyresourcesthroughhardware,thusallowingthesystem

designertotalflexibilityinsystemarchitecture.

An advantage of using semaphores rather than the more common

methodsofhardwarearbitrationisthatwaitstatesareneverincurredin

either processor. This can prove to be a major advantage in very high-

speedsystems.

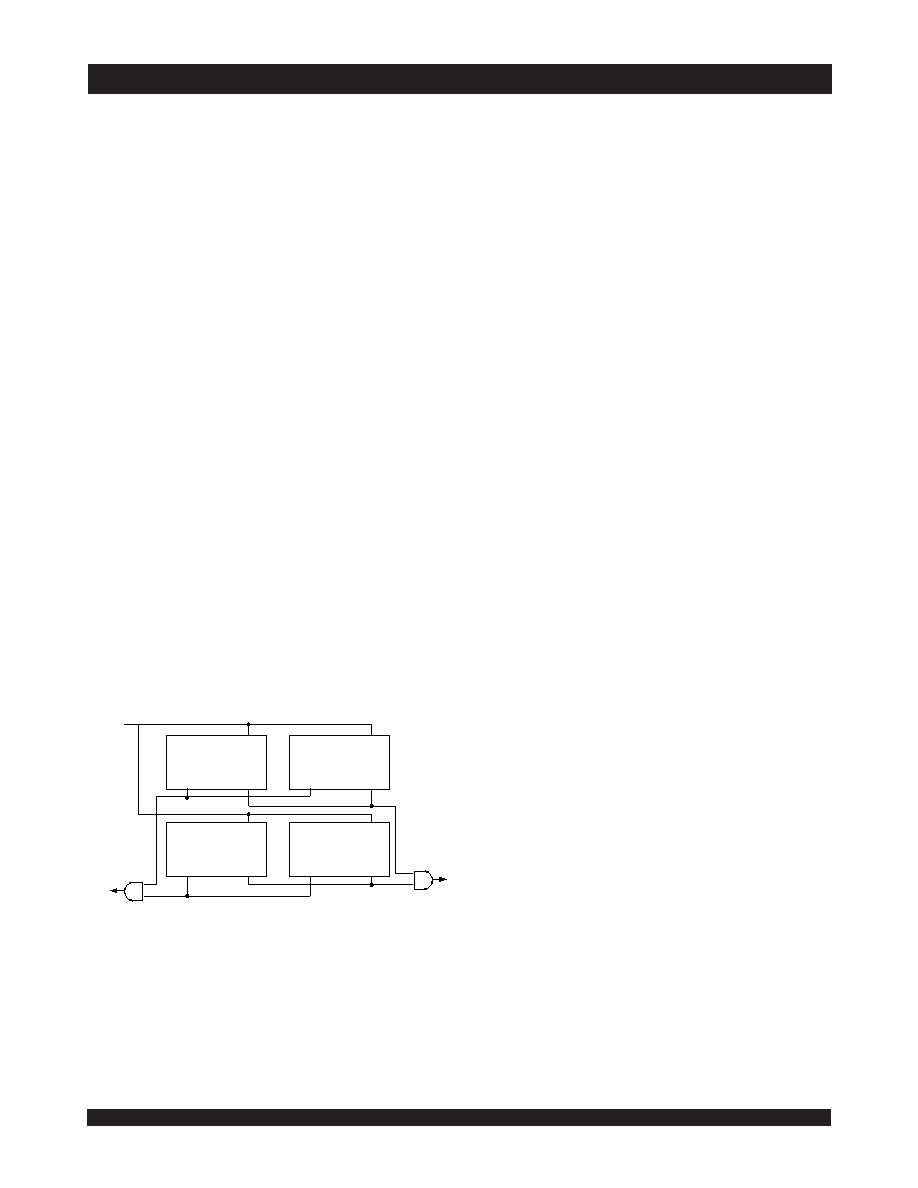

4869 drw 18

MASTER

Dual Port RAM

BUSYR

CE0

MASTER

Dual Port RAM

BUSYR

SLAVE

Dual Port RAM

BUSYR

SLAVE

Dual Port RAM

BUSYR

CE1

CE0

A17(1,2)

BUSYL

.

a"don'tcare".Likewise,therightportinterruptflag(INTR)isassertedwhen

theleftportwritestomemorylocation1FFFF(HEX)(FFFFforIDT70V658

and7FFFforIDT70V657)andtocleartheinterruptflag(INTR),theright

port must read the memory location 1FFFF (FFFF for IDT70V658 and

7FFF for IDT70V657). The message (36 bits) at 1FFFE (FFFE for

IDT70V658 and 7FFE for IDT70V657)or 1FFFF (FFFF for IDT70V658

and 7FFF for IDT70V657) is user-defined since it is an addressable

SRAM location. If the interrupt function is not used, address locations

1FFFE (FFFE for IDT70V658 and 7FFE for IDT70V657) and 1FFFF

(FFFF for IDT70V658 and 7FFF for IDT70V657) are not used as mail

boxes,butaspartoftherandomaccessmemory.RefertoTruthTableIII

fortheinterruptoperation.

Width Expansion with Busy Logic

Master/Slave Arrays

When expanding an IDT70V659/58/57 RAM array in width while

usingBUSYlogic,onemasterpartisusedtodecidewhichsideoftheRAMs

array will receive a BUSY indication, and to output that indication. Any

Figure 3. Busy and chip enable routing for both width and depth

expansion with IDT70V659/58/57 RAMs.

numberofslavestobeaddressedinthesameaddressrangeasthemaster

usetheBUSYsignalasawriteinhibitsignal.ThusontheIDT70V659/58/

57RAMtheBUSYpinisanoutputifthepartisusedasamaster(M/Spin

= VIH), and the BUSY pin is an input if the part used as a slave (M/S pin

= VIL) as shown in Figure 3.

NOTES:

1. A16 for IDT70V658.

2. A15 for IDT70V657.

相關PDF資料 |

PDF描述 |

|---|---|

| 7P12FLV262C25 | 6M X 16 FLASH 3V PROM CARD, 250 ns, XMA68 |

| 7P12FLV520I15 | 6M X 16 FLASH 3V PROM CARD, 150 ns, XMA68 |

| 7P24FLV251I25 | 12M X 16 FLASH 3V PROM CARD, 250 ns, XMA68 |

| 7P24FLV280I15 | 12M X 16 FLASH 3V PROM CARD, 150 ns, XMA68 |

| 7P24FLV570I25 | 12M X 16 FLASH 3V PROM CARD, 250 ns, XMA68 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 70V659S10DRG | 功能描述:IC SRAM 4MBIT 208QFP 制造商:idt, integrated device technology inc 系列:* 零件狀態:在售 標準包裝:6 |

| 70V659S12BC | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Async Dual 3.3V 4.5M-Bit 128K x 36 12ns 256-Pin CABGA Tray 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 4.5MBIT 128KX36 12NS 256BGA - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:128Kx36 STD-PWR 3.3V DUAL-PORT RAM |

| 70V659S12BC8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Async Dual 3.3V 4.5M-Bit 128K x 36 12ns 256-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 4.5MBIT 128KX36 12NS 256BGA - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:128Kx36 STD-PWR 3.3V DUAL-PORT RAM |

| 70V659S12BCGI | 功能描述:靜態隨機存取存儲器 128Kx36 STD-PWR 3.3V DUAL-PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V659S12BCI | 功能描述:靜態隨機存取存儲器 128Kx36 STD-PWR 3.3V DUAL-PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發布緊急采購,3分鐘左右您將得到回復。