- 您現在的位置:買賣IC網 > PDF目錄68812 > 71M6543H-IGTR/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, PQFP100 PDF資料下載

參數資料

| 型號: | 71M6543H-IGTR/F |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 模擬信號調理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 封裝: | LEAD FREE, LQFP-100 |

| 文件頁數: | 119/157頁 |

| 文件大小: | 2178K |

| 代理商: | 71M6543H-IGTR/F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁當前第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁

71M6543F/H and 71M6543G/GH Data Sheet

64

2008–2011 Teridian Semiconductor Corporation

v1.2

A small amount of power can be saved by programming the LCD frequency to the lowest value that

provides satisfactory LCD visibility over the required temperature range.

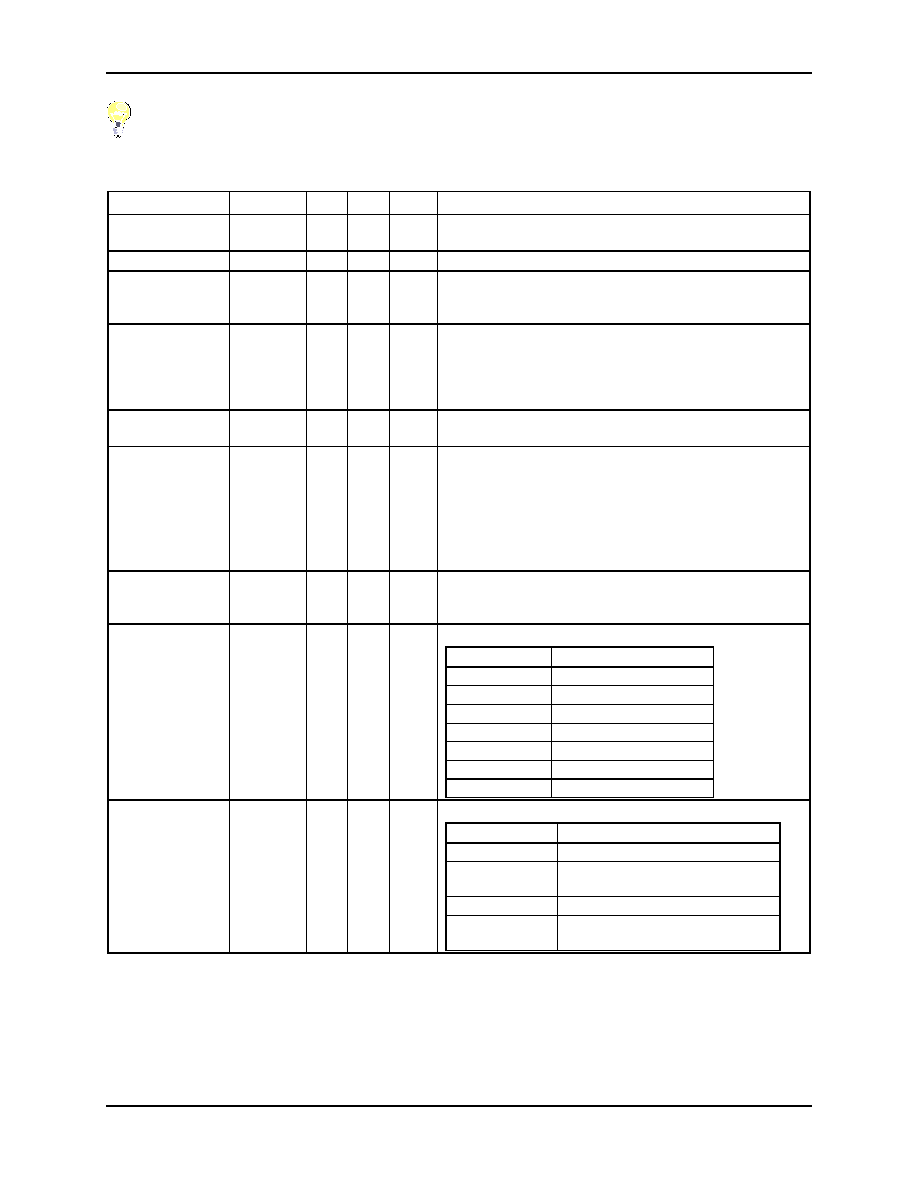

Table 53 shows all I/O RAM registers that control the operation of the LCD interface.

Table 53: LCD Configurations

Name

Location

Rst

Wk

Dir

Description

LCD_ALLCOM

2400[3]

0

–

R/W

Configures all 6 SEG/COM pins as COM. Has no effect

on pins whose LCD_MAP bit is zero.

LCD_BAT

2402[7]

0

–

R/W Connects the LCD power supply to VBAT in all modes.

LCD_E

2400[7]

0

–

R/W

Enables the LCD display. When disabled, VLC2,

VLC1, and VLC0 are ground as are the COM and SEG

outputs if their LCD_MAP bit is 1.

LCD_ON

LCD_BLANK

240C[0]

240C[1]

0

–

R/W

LCD_ON = 1 turns on all LCD segments without

affecting the LCD data. Similarly, LCD_BLANK = 1

turns off all LCD segments without affecting the LCD

data. If both bits are set, all LCD segments are turned

on.

LCD_RST

240C[2]

0

–

R/W

Clear all bits of LCD data. These bits affect SEGDIO

pins that are configured as LCD drivers.

LCD_DAC[4:0]

240D[4:0]

0

–

R/W

This register controls the LCD contrast DAC which

adjusts the VLCD voltage and has an output range of

2.65 VDC to 5.3 VDC. The VLCD voltage is

VLCD = 2.65 + 2.65 * LCD_DAC[4:0]/31

Thus, the LSB of the DAC is 85.5 mV. The maximum

DAC output voltage is limited by V3P3SYS, VBAT, and

whether LCD_BSTE is set.

LCD_CLK[1:0]

2400[1:0]

0

–

R/W

Sets the LCD clock frequency (1/T). See definition of T

in Figure 17.

Note: fw = 32768 Hz

00-fw/2^9, 01-fw/2^8, 10-fw/2^7, 11-fw/2^6

LCD_MODE[2:0]

2400[6:4]

0

–

R/W

The LCD bias and multiplex mode.

LCD_MODE

Output

000

4 states, 1/3 bias

001

3 states, 1/3 bias

010

2 states, bias

011

3 states, bias

100

Static display

101

5 states, 1/3 bias

110

6 states, 1/3 bias

LCD_VMODE[1:0]

2401[7:6]

00

R/W

This register specifies how VLCD is generated.

LCD_VMODE

Description

11

External VLCD

10

LCD boost and LCD DAC

enabled

01

LCD DAC enabled

00

No boost and no DAC.

VLCD = VBAT or V3P3SYS

The LCD can be driven in static, bias, and 1/3 bias modes. Figure 17 defines the COM waveforms.

Note that COM pins that are not required in a specific mode maintain a segment off state rather than

GND, VCC, or high impedance.

The segment drivers SEGDIO22 and SEGDIO23 can be configured to blink at either 0.5 Hz or 1 Hz.

The blink rate is controlled by LCD_Y (I/O RAM 0x2400[2]). There can be up to six pixels/segments

connected to each of these driver pins. The I/O RAM fields LCD_BLKMAP22[5:0] (I/O RAM 0x2402[5:0])

and LCD_BLKMAP23[5:0] (I/O RAM 0x2401[5:0]) identify which pixels, if any, are to blink.

LCD_BLKMAP22[5:0] and LCD_BLKMAP23[5:0] are non-volatile.

相關PDF資料 |

PDF描述 |

|---|---|

| 71M6543F-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543H-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543G-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543GH-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543GH-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 71M6543HT-IGT/F | 制造商:Maxim Integrated Products 功能描述:ENERGY METER ICS - Rail/Tube |

| 71M6543HT-IGTR/F | 制造商:Maxim Integrated Products 功能描述:3-PHASE SOC, 64KB FLASH, PRES TEMP SENSOR, HIGH PRES REF - Tape and Reel |

| 71M6545 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Four-Quadrant Metering, Phase Metrology Processors Flash/RAM Size |

| 71M6545H | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Four-Quadrant Metering, Phase Metrology Processors Flash/RAM Size |

| 71M6545HT-IGT/F | 制造商:Maxim Integrated Products 功能描述:METROLOGY PROCESSORS - Rail/Tube |

發布緊急采購,3分鐘左右您將得到回復。