- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373911 > AD7641 (Analog Devices, Inc.) 18-Bit, 2 MSPS SAR ADC PDF資料下載

參數(shù)資料

| 型號(hào): | AD7641 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 18-Bit, 2 MSPS SAR ADC |

| 中文描述: | 18位,2 MSPS的SAR型ADC |

| 文件頁數(shù): | 20/24頁 |

| 文件大小: | 324K |

| 代理商: | AD7641 |

AD7641

Preliminary Technical Data

Rev. Pr E | Page 20 of 24

SCLK

SDOUT

D17

D16

D1

D0

D15

X17

X16

X15

X

1

X0

Y17

Y16

CS

BUSY

SDIN

EXT/INT = 1

INVSCLK = 0

t

35

t

36

t

37

t

31

t

32

t

16

t

33

t

34

X17

X16

X

1

2

20

RD = 0

18

17

3

4

19

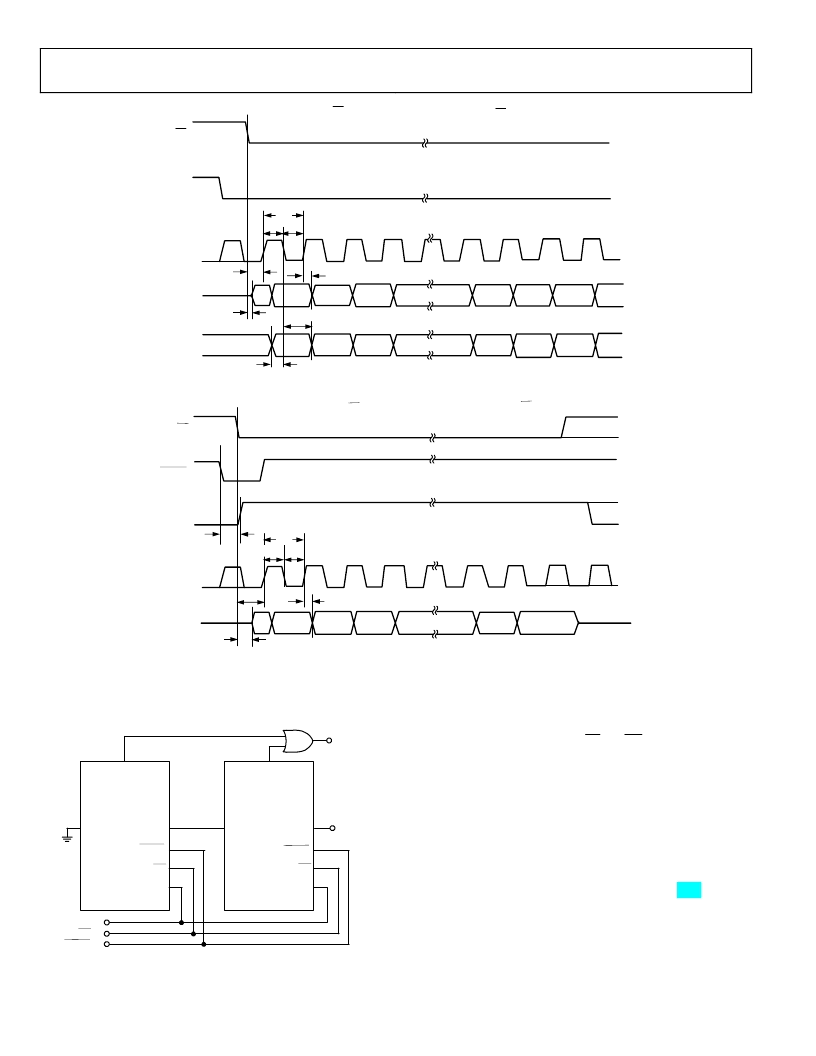

Figure 21. Slave Serial Data Timing for Reading (Read After Convert)

SDOUT

CS

SCLK

D1

D0

X

D17

D16

D15

1

2

3

16

17

18

t

3

t

35

t

36

t

37

t

31

t

32

t

16

CNVST

BUSY

EXT/INT = 1

INVSCLK = 0

RD =0

Figure 22. Slave Serial Data Timing for Reading (Read Previous Conversion During Convert)

CNVST

CS

SCLK

SDOUT

RDC/SDIN

BUSY

BUSY

DATA

OUT

AD7641

#1

(DOWNSTREAM)

BUSY

OUT

CNVST

CS

SCLK

AD7641

#2

(UPSTREAM)

RDC/SDIN

SDOUT

SCLK IN

CS IN

CNVST IN

Figure 23. Two AD7641 in a “Daisy-Chain” Configuration

External Clock Data Read During Conversion

Figure 22 shows the detailed timing diagrams of this method.

During a conversion, while both CS and RD are both low, the

result of the previous conversion can be read. The data is shifted

out, MSB first, with 18 clock pulses and is valid on both rising

and falling edge of the clock. The 18 bits have to be read before

the current conversion is complete. If that is not done,

RDERROR is pulsed high and can be used to interrupt the host

interface to prevent incomplete data reading. There is no “daisy

chain” feature in this mode and RDC/SDIN input should always

be tied either high or low. To reduce performance degradation

due to digital activity, a fast discontinuous clock of TBD is

recommended to ensure that all the bits are read during the first

half of the conversion phase. It is also possible to begin to read

the data after conversion and continue to read the last bits even

after a new conversion has been initiated.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7641ACP | 18-Bit, 2 MSPS SAR ADC |

| AD7641ACPRL | ECONOLINE: REC2.2-S_DRW(Z)/H* - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- 4.5-9V, 9-18V, 18-36V, 36-72V Wide Input Range 2 : 1- UL94V-0 Package Material- Continuous Short Circiut Protection- Cost Effective- 100% Burned In- Efficiency to 84% |

| AD7641AST | 18-Bit, 2 MSPS SAR ADC |

| AD7641ASTRL | 18-Bit, 2 MSPS SAR ADC |

| AD7650 | 16-Bit 1 MSPS SAR Unipolar ADC with Ref |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7641ACP | 制造商:Analog Devices 功能描述:ADC SGL SAR 2MSPS 18BIT PARALLEL/SERL 48LFCSP - Trays |

| AD7641ACPRL | 制造商:Analog Devices 功能描述:ADC SGL SAR 2MSPS 18BIT PARALLEL/SERL 48LFCSP - Tape and Reel |

| AD7641AST | 制造商:Analog Devices 功能描述:ADC SGL SAR 2MSPS 18BIT PARALLEL/SERL 48LQFP - Bulk |

| AD7641ASTRL | 制造商:Analog Devices 功能描述:ADC SGL SAR 2MSPS 18BIT PARALLEL/SERL 48LQFP - Tape and Reel |

| AD7641BCPZ | 功能描述:IC ADC 18BIT 2MSPS SAR 48-LFCSP RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 其它有關(guān)文件:TSA1204 View All Specifications 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):12 采樣率(每秒):20M 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:2 功率耗散(最大):155mW 電壓電源:模擬和數(shù)字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應(yīng)商設(shè)備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數(shù)目和類型:4 個(gè)單端,單極;2 個(gè)差分,單極 產(chǎn)品目錄頁面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。