- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373913 > AD7679CB1 (Analog Devices, Inc.) 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC PDF資料下載

參數(shù)資料

| 型號(hào): | AD7679CB1 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC |

| 中文描述: | 18位,2.5 LSB INL和570 kSPS的SAR型ADC |

| 文件頁(yè)數(shù): | 20/28頁(yè) |

| 文件大小: | 506K |

| 代理商: | AD7679CB1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

AD7679

DIGITAL INTERFACE

The AD7679 has a versatile digital interface; it can be interfaced

with the host system by using either a serial or parallel interface.

The serial interface is multiplexed on the parallel data bus. The

AD7679 digital interface also accommodates both 3 V and 5 V

logic by simply connecting the AD7679’s OVDD supply pin to

the host system interface digital supply. Finally, by using the

OB/2C input pin in any mode but 18-bit interface mode, both

twos complement and straight binary coding can be used.

Rev. 0 | Page 20 of 28

The two signals, CS and RD, control the interface. When at least

one of these signals is high, the interface outputs are in high

impedance. Usually, CS allows the selection of each AD7679 in

multicircuit applications, and is held low in a single AD7679

design. RD is generally used to enable the conversion result on

the data bus.

t

9

RESET

DATA

BUS

BUSY

CNVST

t

8

03085-0-035

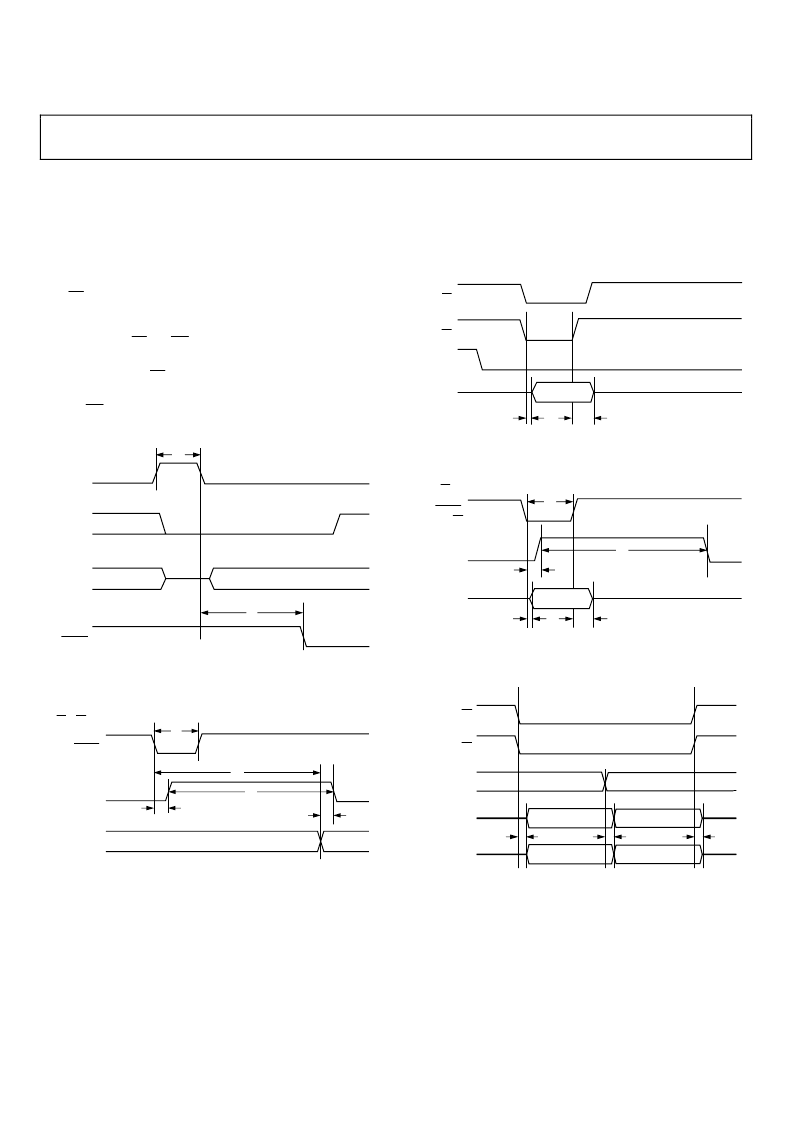

Figure 33. RESET Timing

CNVST

BUSY

DATA

BUS

CS = RD = 0

PREVIOUS CONVERSION DATA

NEW DATA

t

1

t

10

t

4

t

3

t

11

03085-0-036

Figure 34. Master Parallel Data Timing for Reading (Continuous Read)

PARALLEL INTERFACE

The AD7679 is configured to use the parallel interface with an

18-bit, a 16-bit, or an 8-bit bus width, according to Table 7. The

data can be read either after each conversion, which is during

the next acquisition phase, or during the following conversion,

as shown in Figure 35 and Figure 36, respectively. When the

data is read during the conversion, however, it is recommended

that it is read only during the first half of the conversion phase.

This avoids any potential feedthrough between voltage

transients on the digital interface and the most critical analog

conversion circuitry. Refer to Table 7 for a detailed description

of the different options available.

DATA

BUS

t

12

t

13

BUSY

CS

RD

CURRENT

CONVERSION

03085-0-037

Figure 35. Slave Parallel Data Timing for Reading (Read after Convert)

CS = 0

CNVST,

RD

t

1

PREVIOUS

CONVERSION

DATA

BUS

t

12

t

13

BUSY

t

4

t

3

03085-0-038

Figure 36. Slave Parallel Data Timing for Reading (Read during Convert)

CS

RD

A0, A1

PINS D[15:8]

PINS D[7:0]

HI-Z

HI-Z

HIGH BYTE

LOW BYTE

LOW BYTE

HIGH BYTE

HI-Z

HI-Z

t

12

t

12

t

13

03085-0-039

Figure 37. 8-Bit and 16-Bit Parallel Interface

SERIAL INTERFACE

The AD7679 is configured to use the serial interface when

MODE0 and MODE1 are held high. The AD7679 outputs 18

bits of data, MSB first, on the SDOUT pin. This data is

synchronized with the 18 clock pulses provided on the SCLK

pin. The output data is valid on both the rising and falling edge

of the data clock.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7694 | 16-Bit, 250 kSPS PulSAR ADC in MSOP |

| AD7694ARM | 16-Bit, 250 kSPS PulSAR ADC in MSOP |

| AD7694ARMRL7 | 16-Bit, 250 kSPS PulSAR ADC in MSOP |

| AD7694BRM | 16-Bit, 250 kSPS PulSAR ADC in MSOP |

| AD7694BRMRL7 | 16-Bit, 250 kSPS PulSAR ADC in MSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD767A | 制造商:AD 制造商全稱:Analog Devices 功能描述:Microprocessor-Compatible 12-Bit D/A Converter |

| AD767ACHIPS | 制造商:AD 制造商全稱:Analog Devices 功能描述:Microprocessor-Compatible 12-Bit D/A Converter |

| AD767AD | 功能描述:IC DAC 12BIT W/AMP 24-CDIP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 數(shù)模轉(zhuǎn)換器 系列:- 產(chǎn)品培訓(xùn)模塊:Data Converter Fundamentals DAC Architectures 標(biāo)準(zhǔn)包裝:750 系列:- 設(shè)置時(shí)間:7µs 位數(shù):16 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 電壓電源:雙 ± 功率耗散(最大):100mW 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-LCC(J 形引線) 供應(yīng)商設(shè)備封裝:28-PLCC(11.51x11.51) 包裝:帶卷 (TR) 輸出數(shù)目和類型:1 電壓,單極;1 電壓,雙極 采樣率(每秒):143k |

| AD767BD | 功能描述:IC DAC 12BIT W/AMP 24-CDIP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 數(shù)模轉(zhuǎn)換器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1,000 系列:- 設(shè)置時(shí)間:1µs 位數(shù):8 數(shù)據(jù)接口:串行 轉(zhuǎn)換器數(shù)目:8 電壓電源:雙 ± 功率耗散(最大):941mW 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應(yīng)商設(shè)備封裝:24-SOIC W 包裝:帶卷 (TR) 輸出數(shù)目和類型:8 電壓,單極 采樣率(每秒):* |

| AD767JN | 功能描述:IC DAC 12BIT 24-DIP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 數(shù)模轉(zhuǎn)換器 系列:- 產(chǎn)品培訓(xùn)模塊:Data Converter Fundamentals DAC Architectures 標(biāo)準(zhǔn)包裝:750 系列:- 設(shè)置時(shí)間:7µs 位數(shù):16 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 電壓電源:雙 ± 功率耗散(最大):100mW 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-LCC(J 形引線) 供應(yīng)商設(shè)備封裝:28-PLCC(11.51x11.51) 包裝:帶卷 (TR) 輸出數(shù)目和類型:1 電壓,單極;1 電壓,雙極 采樣率(每秒):143k |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。