- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9853 (Analog Devices, Inc.) Programmable Digital QPSK/16-QAM Modulator(可編程數字的四相移鍵控/16-正交幅度調制的調節器) PDF資料下載

參數資料

| 型號: | AD9853 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Programmable Digital QPSK/16-QAM Modulator(可編程數字的四相移鍵控/16-正交幅度調制的調節器) |

| 中文描述: | 可編程數字QPSK/16-QAM調制器(可編程數字的四相移鍵控/ 16 -正交幅度調制的調節器) |

| 文件頁數: | 28/31頁 |

| 文件大小: | 339K |

| 代理商: | AD9853 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁

AD9853

–28–

REV. A

C33

10

m

F

+10V

FEC (SW2) FUNCTIONS

JUMPER

1-2

FUNCTION

SOFT FEC

ENABLE/DISABLE

HARD FEC DISABLE

HARD FEC ENABLE

OR EXTERNAL FEC

CONTROL VIA J11

2-3

OPEN

WHEN USING

TRANSFORMER T1A,

REMOVE R3 AND R6

WHEN NOT USING T1A,

CONNECT E13 TO E14

AND LEAVE R3 AND

R6 IN PLACE

TST1

HI 4DM

J9

2

4

6

8

10

12

14

1

3

5

7

9

11

13

REST

CAE

E13

T1A

T1 – 1T

4

SIG

R6

25

V

2

6

1 : 1

E14

GND

23

C

A

I

I

T

T

T

T

T

T

R

AVDD

DAC BL

AVDD

AGND

DAC RSET

NC

AGND

PLL FILTER

PLL VCC

PLL GND

GND

CA CLK

CA DATA

DGND

DVDD

REF CLK IN

DGND

DVDD

DATA IN

TX ENABLE

DVDD

DGND

D

D

B

F

A

D

D

D

D

T

B

AD9853

U1

34

35

36

37

38

39

40

41

42

43

CAC

CAD

DUT+V

CLK

DUT+V

SDI

TXE

DUT+V

44

TST1

SMB

J10

EXTERNAL

FEC ENABLE

R7

3.9k

V

+5V

FECC

1 2 3

SW2

H3M

DIGITAL

MODULATOR

22

12

21

20

19

18

17

16

15

14

13

C31

0.1

m

F

R4

3.9k

V

DUT+V

C10

0.01

m

F

33

32 31 30 29 28 27 26 25 24

D

B

B

GND

1

3

DUT+V

DUT+V

GND

DUT+V

GND

1R5

V

D

NOTE:

C31 NORMALLY

NOT POPULATED

1

11

2

3

4

5

6

7

8

9

10

C25

0.1

m

F

DUT+V

C24

0.1

m

F

DUT+V

C23

0.1

m

F

DUT+V

C30

0.1

m

F

DUT+V

C29

0.1

m

F

DUT+V

DAC OUT/

FILTER IN

SMB

J6

E9

E1

E10

SIG

E2

SIG

R3

50

V

C6

68pF

(33pF)

C3

7pF

(6.8pF)

1

2

C9

56pF

(39pF)

E3 E4

E11 E12

AMP

SMB

J7

FILTER OUT/

AMP IN

C7

100pF

(82pF)

C4

33pF

(33pF)

C5

22pF

(27pF)

C8

82pF

(82pF)

L1

120NH

(180NH)

L2

100NH

(100NH)

1

L3

100NH

(150NH)

1

2

2

7TH ORDER ELIPTIC 50

LOW PASS FILTER

VALUES IN PARENTHESES – 45 MHz FILTER

VALUES NOT IN PARENTHESES – 65 MHz FILTER

T

ENABLE

JUMPER CONFIGURATION

JUMPER

E5-E6

FUNCTION

HEADER CONNECTOR

FROM DG2020,

DATA GENERATOR

SOFTWARE CONTROL

OF T

X

ENABLE

HARD ENABLE OR

EXT. CONTROL VIA J4

E7-E8

OPEN

T

X

ENABLE

E7 E5

TXEE

E8 E6SMB

J4

R11

3.9k

V

+5V

TXE

GND

+5V

C17

0.1

m

F

Y1

14

VCC

OUT

8

GND

7

SW41

CLK

SMB

J2

R1

50

V

EXTERNAL

CLK

CRYSTAL OSC.

IF CLOCK

REMOVE SOURCE IS

Y1 J2 (EXTERNAL)

R1 Y1 (XTAL)

JUMPER FUNCTION

1-2

HARD POWER-DOWN

2-3

HARD POWER-DOWN

OR EXTERNAL CONTROL

VIA J3

NO

JUMPER

POWERED UP

AD8320 POWER-DOWN

SW1 FUNCTIONS

8PPT+5V

RZ1

2

3

4

5

6

7

8

LATCH

BUSCLK

BUSDAT

RESET

TXEN

BDAT

TSTATE

2.2k PULL-UP

NETWORK

TO +5V

THREE-STATE BUFFER

U4

74AC244

2A4 2Y4

2A3 2Y3

2A2 2Y3

2A1 2Y2

1A4 1Y4

1A3 1Y3

1A2 1Y2

1A1 1Y1

1G 2G

17

15

13

11

8

6

4

2

GND

GND

GND

BDAT

DAT

3

5

7

9

12

14

16

18

RBAK

BDAT

TSTAT

19

1

+5V

C22

0.1

m

F

LATCH

U3

74ACT573

+5V

R8

3.9k

V

FEC

9

8

7

6

5

4

3

2

TXEN

TSTATE

RESET

BUSDAT

BUSCLK

12

13

14

15

16

17

18

19

FECC

TXEE

TSAT

REST

DAT

BCLK

+5V

11

1

LATCH

C34

0.001

m

F

8D 8Q

7D 7Q

6D 6Q

5D 5Q

4D 4Q

3D 3Q

2D 2Q

1D 1Q

EN OE

C21

0.1

m

F

"CENTRONICS"

PRINT PORT

CONN.

C36CRPX

J1

LATCH

BUSCLK

BUSDAT

RESET

FEC

TXEN

TSTATE

RBAK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

C20

10

m

F

+10V

TB1

POWER INPUT

CONNECTOR

DUT+V

GND

+5V

GND

+10V

1

2

3

4

5

75

V

OUTPUT

SMB 75

J8

C12

0.1

m

F

C2

0.1

m

F

VCCL

VIN

VREF

VCC

GND

GND

BYP

GND

GND

GND

20

19

18

17

16

15

14

13

12

11

+10V

+10V

CAD

CAC

CAE

GND

PDN

+10V

+10V

+10V

C32

0.1

m

F

PROGRAMMABLE

GAIN AMPLIFIER

C1

0.1

m

F

C11

0.1

m

F

R2

62

V

AMP

SDATA

CLK

DATEN

GND

VOCM

PD

VCC

VCC

VCC

VOUT

AD8320

U2

1

2

3

4

5

6

7

8

9

10

C16

0.1

m

F

+10V

SERIAL DATA IN

SDI

SMB

J5

R12

3.9k

V

+5V

SDI

SMB

J3

PODN

R10

3.9k

V

AD8320

EXTERNAL

POWERDOWN

1

2

3

GND

PDN

PODN

H3M

SW1

AD8320

POWERDOWN

SOURCE

SWITCH

C26

0.1

m

F

DUT+V

C27

0.1

m

F

DUT+V

C28

0.1

m

F

DUT+V

C15

0.1

m

F

+10V

C19

10

m

F

DUT+V

C13

10

m

F

+10V

C14

0.1

m

F

+10V

C18

10

m

F

+5V

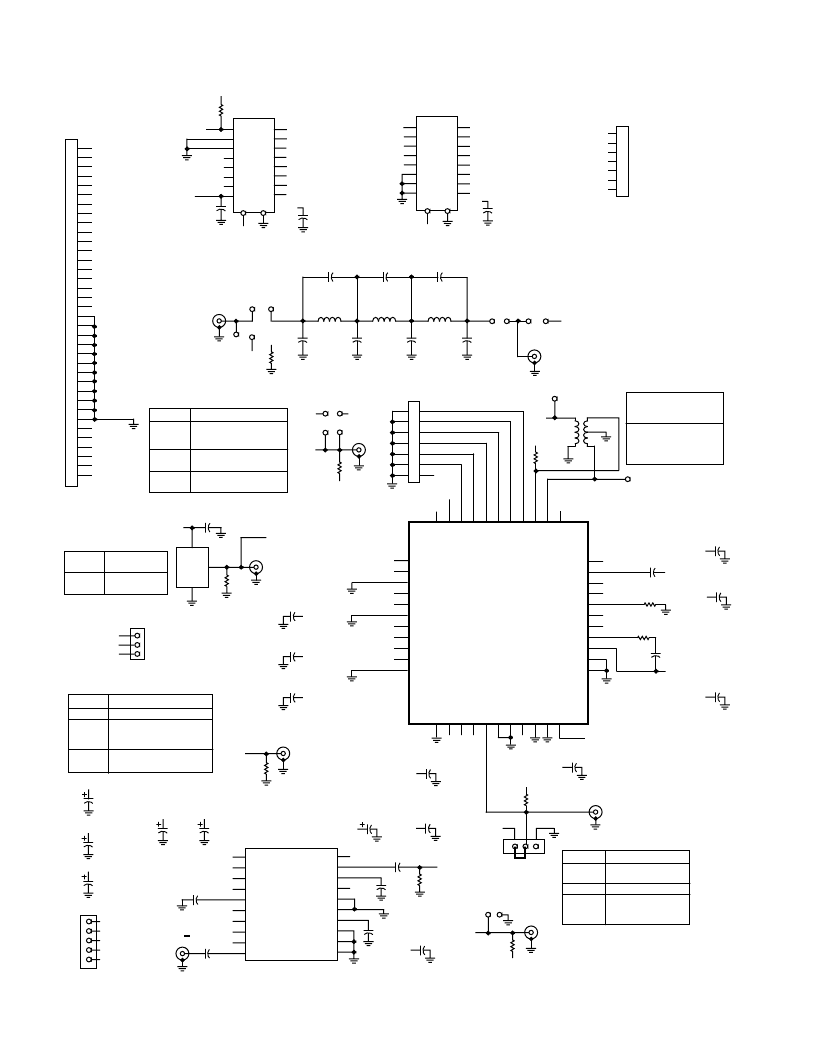

Figure 39. Electrical Schematic of AD9853-xxPCB Evaluation Board

相關PDF資料 |

PDF描述 |

|---|---|

| AD9854 | CMOS 300MHz Quadrature Complete-DDS |

| AD9858TLPCB | 1 GSPS Direct Digital Synthesizer |

| AD9858BSV | 1 GSPS Direct Digital Synthesizer |

| AD9858PCB | 1 GSPS Direct Digital Synthesizer |

| AD9858 | 1 GSPS Direct Digital Synthesizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9853-45PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:Programmable Digital OPSK/16-QAM Modulator |

| AD9853-65PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:Programmable Digital OPSK/16-QAM Modulator |

| AD9853AS | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD9854 | 制造商:AD 制造商全稱:Analog Devices 功能描述:CMOS 300 MHz Quadrature Complete-DDS |

| AD9854/PCB | 制造商:Analog Devices 功能描述:Evaluation Board For IC Digital Synthesizer Single 制造商:Analog Devices 功能描述:Direct Digital Synthesizer IC (DDS) |

發布緊急采購,3分鐘左右您將得到回復。