- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373969 > AD9858FDPCB (Analog Devices, Inc.) 1 GSPS Direct Digital Synthesizer PDF資料下載

參數(shù)資料

| 型號: | AD9858FDPCB |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | XO, clock |

| 英文描述: | 1 GSPS Direct Digital Synthesizer |

| 中文描述: | 1 GSPS的直接數(shù)字頻率合成器 |

| 文件頁數(shù): | 20/32頁 |

| 文件大小: | 1412K |

| 代理商: | AD9858FDPCB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

AD9858

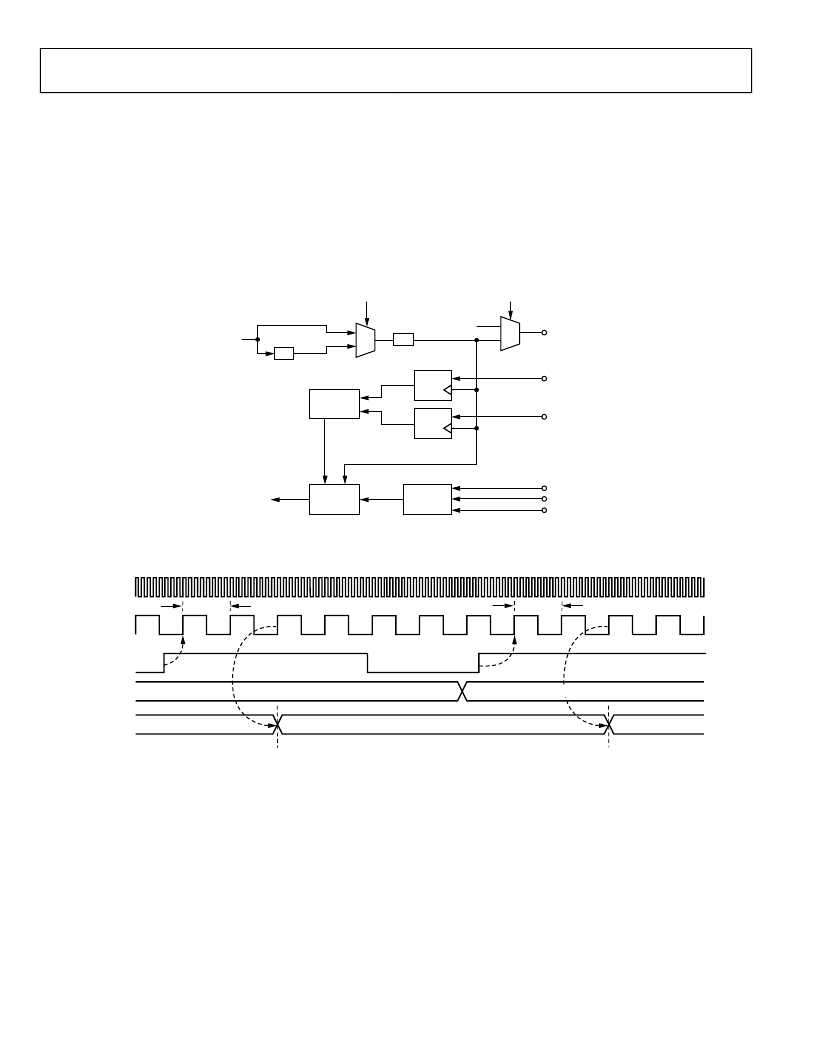

SYSCLK serves as the sample clock for the DAC and is fed to a

divide-by-8 frequency divider to produce SYNCLK. SYNCLK is

provided to the user on the SYNCLK pin. This enables

synchronization of external hardware with the AD9858’s

internal DDS clock. External hardware that is synchronized to

the SYNCLK signal can then be used to provide the frequency

update (FUD) signal to the AD9858. The FUD signal and

SYNCLK are used to transfer the internal buffer register

contents into the memory registers of the device. Figure 33

Rev. A | Page 20 of 32

shows a block diagram of the synchronization methodology,

and Figure 34 shows an I/O synchronization timing diagram.

Note that SYNCLK is also used to synchronize the assertion of

the profile select pins (PS0, PS1). The FUD, PS0, and PS1 pins

must be set up and held around the rising edge of SYNCLK.

These device inputs are designed for zero hold time and 3.5 ns

setup time.

U

REGISTER

MEMORY

EDGE

DETECTION

LOGIC

REFCLK

P0, P1

FUD

SYNCLK

0

2 GHz DIVIDER

DISABLE

SYNCLK

DISABLE

TO CORE LOGIC

BUFFER

MEMORY

÷ 2

1

0

1

0

D

Q

WR

ADDR

DATA

SYNCLK

D

Q

0

÷ 8

Figure 33. I/O Synchronization Block Diagram

SYNCLK

SYSCLK

FUD REGISTERED

FUD EDGE DETECTED

FUD REGISTERED

FUD EDGE DETECTED

VALUE 2

VALUE 1

IO BUFFER

MEMORY

CONTROL

REGISTER

DATA

VALUE 0

VALUE 1

VALUE 2

(ASYNCHRONOUSLY LOADED VIA I/O PORT)

FUD

*

*

FUD IS AN INPUT PROVIDED BY THE USER THAT MUST BE SET UP AND HELD AROUND RISING EDGES OF SYNCLK. THE OCCURRENCE OF

THE RISING EDGE OF SYNCLK DURING THE HIGH STATE OF THE UPDATEREGS SIGNAL CAUSES THE BUFFER MEMORY CONTENTS TO BE

TRANSFERRED INTO THE CONTROL REGISTERS. SIMILARLY, A STATE CHANGE ON THE PS0 OR PS1 PINS IS EQUIVALENT TO ASSERTING A VALID

FUD SEQUENCE. NOTE: I/O UPDATES ARE SYNCHRONOUS TO THE SYNCLK SIGNAL, REGARDLESS OF THE SYNCHRONIZATION MODE SELECTED.

(ASYNCHRONOUSLY LOADED VIA I/O PORT)

0

Figure 34. I/O Synchronization Timing Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9859 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV-REEL7 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9862PCB | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9860 | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9858PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858TLPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858XSV | 制造商:Analog Devices 功能描述: |

| AD9859 | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859/PCB | 制造商:Analog Devices 功能描述:NCO, 400MSPS 10 BIT, 1.8V CMOS DIRECT DGTL SYNTHESIZER - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。