- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9858FDPCB (Analog Devices, Inc.) 1 GSPS Direct Digital Synthesizer PDF資料下載

參數資料

| 型號: | AD9858FDPCB |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | XO, clock |

| 英文描述: | 1 GSPS Direct Digital Synthesizer |

| 中文描述: | 1 GSPS的直接數字頻率合成器 |

| 文件頁數: | 28/32頁 |

| 文件大小: | 1412K |

| 代理商: | AD9858FDPCB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁

AD9858

Phase Offset Control

Rev. A | Page 28 of 32

A 14-bit phase offset (θ) may be added to the output of the

phase accumulator by means of the phase offset words stored in

the memory registers. This feature provides the user with three

different methods of phase control.

The first method is a static phase adjustment, where a fixed

phase offset is loaded into the appropriate phase-offset register

and left unchanged. The result is that the output signal is offset

by a constant angle relative to the nominal signal. This allows

the user to phase align the DDS output with an external signal,

if necessary.

The second method of phase control is where the user regularly

updates the appropriate phase-offset register via the I/O port.

By properly modifying the phase offset as a function of time,

the user can implement a phase modulated output signal. The

rate at which phase modulation can be performed is limited by

both the speed of the I/O port and the frequency of SYSCLK.

The third method of phase control involves the profile registers,

in which the user loads up to four different phase-offset values

into the appropriate profiles. The user can then select among

the four preloaded phase-offset values via the AD9858 profile

select pins. Thus, the phase changes are accomplished by driving

the hardware pins rather than writing to the I/O port, thereby

avoiding the speed limitation imposed by the I/O port.

However, this method is restricted to only four phase-offset

values (one phase-offset value per profile). Each profile has an

associated frequency and phase value. Changing the current

profile updates both parameters, so care must be taken to

ensure that no unwanted parameter changes take place.

Note that the phase-offset value is routed through a unit delay

(z

–1

) block. This is done to ensure that updates of the phase-

offset values exhibit the same amount of latency as updates of

the frequency tuning word. Otherwise, if the user decides to

update both frequency and phase-offset values, the phase-offset

change would propagate through the device before the tuning

word change. The presence of the unit delay in the phase-offset

path ensures that both frequency and phase-offset changes

exhibit similar latency.

Profile Selection

A profile consists of a specific group of memory registers (see

Table 6). In the AD9858 each profile contains a 32-bit frequency

tuning word and a 14-bit phase-offset word. Each profile is

selectable via two external profile select pins (PS0 and PS1) as

defined in Table 12. The specific mapping of registers to profiles

is detailed in the Register Bit Descriptions section. The user

should be aware that selection of a profile is internally

synchronized with DDS CLK using the SYNCLK timing. That

is, SYNCLK is used to synchronize the assertion of the profile

select pins (PS0, PS1). Therefore, the PS0 and PS1 pins must be

set up and held around the rising edge of SYNCLK. The PS0

and PS1 inputs are designed for zero hold time and 3.5 ns

setup time.

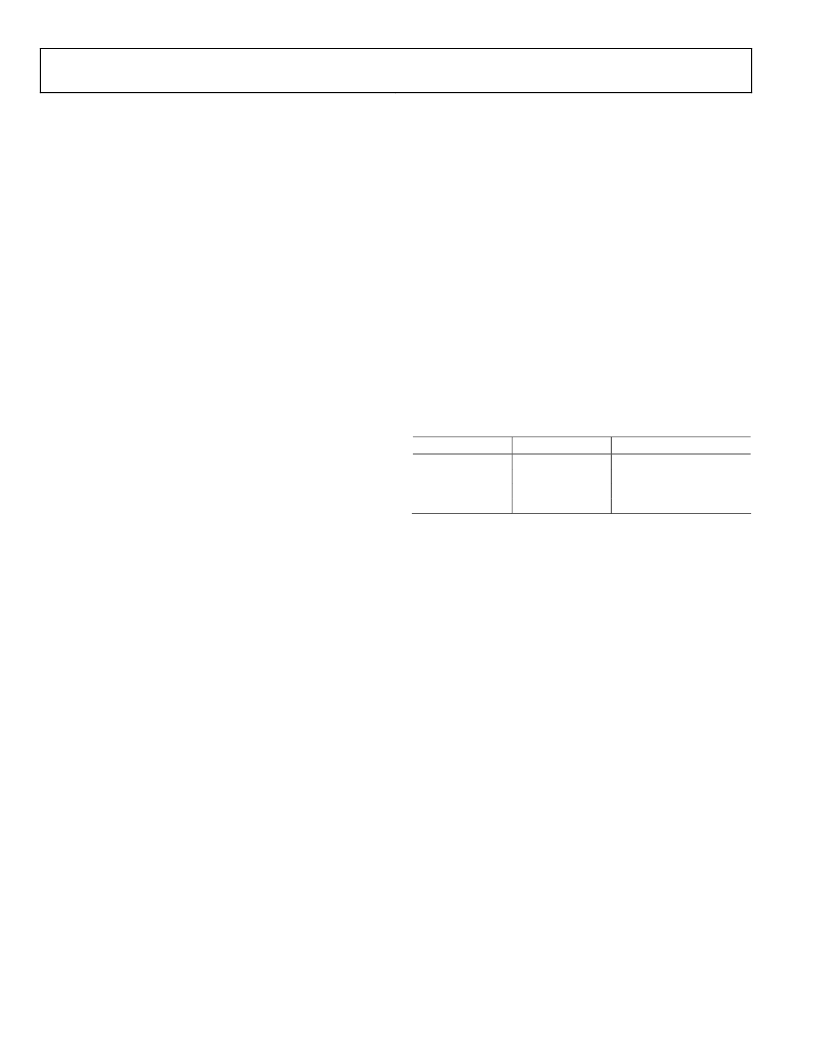

Table 12.

PS1

PS0

0

0

0

1

1

0

1

1

Profile

0

1

2

3

The profiles are available to the user to provide rapid changing

of device parameters via external hardware, which alleviates the

speed limitations imposed by the I/O port. For example, the

user might preprogram the four phase offset registers with

values that correspond to phase increments of 90°. By

controlling the PS0 and PS1 pins, the user can implement

π

/2

phase modulation. The data modulation rate would be much

higher than that possible by repeatedly reloading a single phase-

offset register via the I/O port.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9859 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV-REEL7 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9862PCB | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9860 | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9858PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858TLPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858XSV | 制造商:Analog Devices 功能描述: |

| AD9859 | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859/PCB | 制造商:Analog Devices 功能描述:NCO, 400MSPS 10 BIT, 1.8V CMOS DIRECT DGTL SYNTHESIZER - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。