- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9858FDPCB (Analog Devices, Inc.) 1 GSPS Direct Digital Synthesizer PDF資料下載

參數資料

| 型號: | AD9858FDPCB |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | XO, clock |

| 英文描述: | 1 GSPS Direct Digital Synthesizer |

| 中文描述: | 1 GSPS的直接數字頻率合成器 |

| 文件頁數: | 3/32頁 |

| 文件大小: | 1412K |

| 代理商: | AD9858FDPCB |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

AD9858

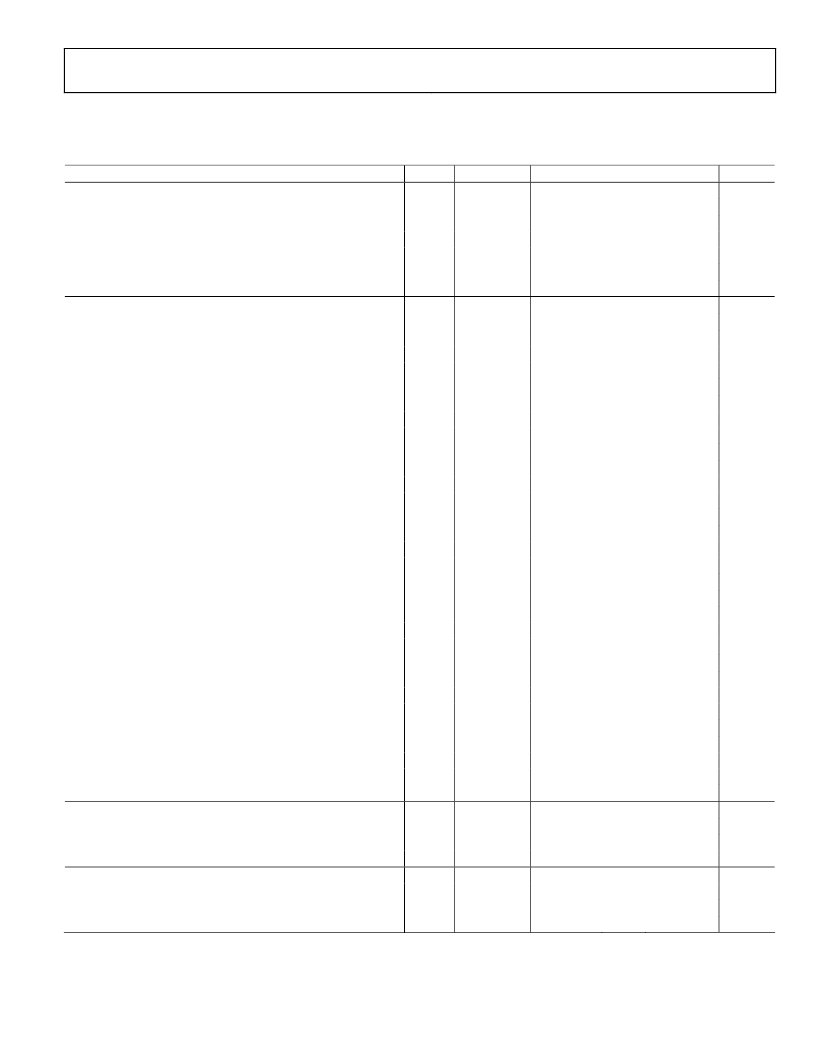

AD9858—ELECTRICAL SPECIFICATIONS

Table 1. Unless otherwise noted, V

DD

= 3.3 V ± 5%, CPV

DD

= 5 V ± 5%, R

SET

= 2 k, C

PISET

= 2.4 k,

Reference Clock Frequency = 1 GHz.

Parameter

REF CLOCK INPUT CHARACTERISTICS

1, 2

Reference Clock Frequency Range (Divider Off)

Reference Clock Frequency Range (Divider On)

Duty Cycle @ 1 GHz

Input Capacitance

Input Impedance

Input Sensitivity

DAC OUTPUT CHARACTERISTICS

Resolution

Full-Scale Output Current

Gain Error

Output Offset

Differential Nonlinearity

Integral Nonlinearity

Output Impedance

Voltage Compliance Range

Wideband SFDR (DC to Nyquist)

40 MHz F

OUT

100 MHz F

OUT

180 MHz F

OUT

360 MHz F

OUT

180 MHz F

OUT

(700 MHz REFCLK)

Narrow-Band SFDR3

3

40 MHz F

OUT

(±15 MHz)

40 MHz F

OUT

(±1 MHz)

40 MHz F

OUT

(±50 kHz)

100 MHz F

OUT

(±15 MHz)

100 MHz F

OUT

(±1 MHz)

100 MHz F

OUT

(±50 kHz)

180 MHz F

OUT

(±15 MHz)

180 MHz F

OUT

(±1 MHz)

180 MHz F

OUT

(±50 kHz)

360 MHz F

OUT

(±15 MHz)

360 MHz F

OUT

(±1 MHz)

360 MHz F

OUT

(±50 kHz)

180 MHz F

OUT

(±15 MHz) (700 MHz REFCLK)

180 MHz F

OUT

(±1 MHz) (700 MHz REFCLK)

180 MHz F

OUT

(±50 kHz) (700 MHz REFCLK)

OUTPUT PHASE NOISE CHARACTERISTICS (@ 103 MHz I

OUT

)

@ 1 kHz Offset

@ 10 kHz Offset

@ 100 kHz Offset

OUTPUT PHASE NOISE CHARACTERISTICS (@ 403 MHz I

OUT

)

@ 1 kHz Offset

@ 10 kHz Offset

@ 100 kHz Offset

Rev. A | Page 3 of 32

Temp

Full

Full

25°C

25°C

25°C

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Test Level

VI

VI

V

V

IV

VI

VI

VI

VI

VI

VI

VI

V

V

V

V

IV

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

Min

10

20

42

–20

5

–10

AV

DD

– 1.5

52

Typ

50

3

1500

10

20

0.5

1

100

60

54

53

50

82

87

88

81

82

86

74

84

85

75

85

86

65

80

84

–147

–150

–152

–133

–137

–140

Max

1000

2000

58

+5

40

+10

15

1

1.5

AV

DD

+ 0.5

Unit

MHz

MHz

%

pF

dBm

Bits

mA

% FS

μA

LSB

LSB

k

V

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

相關PDF資料 |

PDF描述 |

|---|---|

| AD9859 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV-REEL7 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9862PCB | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9860 | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9858PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858TLPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858XSV | 制造商:Analog Devices 功能描述: |

| AD9859 | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859/PCB | 制造商:Analog Devices 功能描述:NCO, 400MSPS 10 BIT, 1.8V CMOS DIRECT DGTL SYNTHESIZER - Bulk |

發布緊急采購,3分鐘左右您將得到回復。