- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373969 > AD9860PCB (Analog Devices, Inc.) Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications PDF資料下載

參數(shù)資料

| 型號(hào): | AD9860PCB |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| 中文描述: | 混合寬帶通信信號(hào)前端(MxFE⑩)處理器 |

| 文件頁(yè)數(shù): | 4/32頁(yè) |

| 文件大小: | 617K |

| 代理商: | AD9860PCB |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

REV. 0

–4–

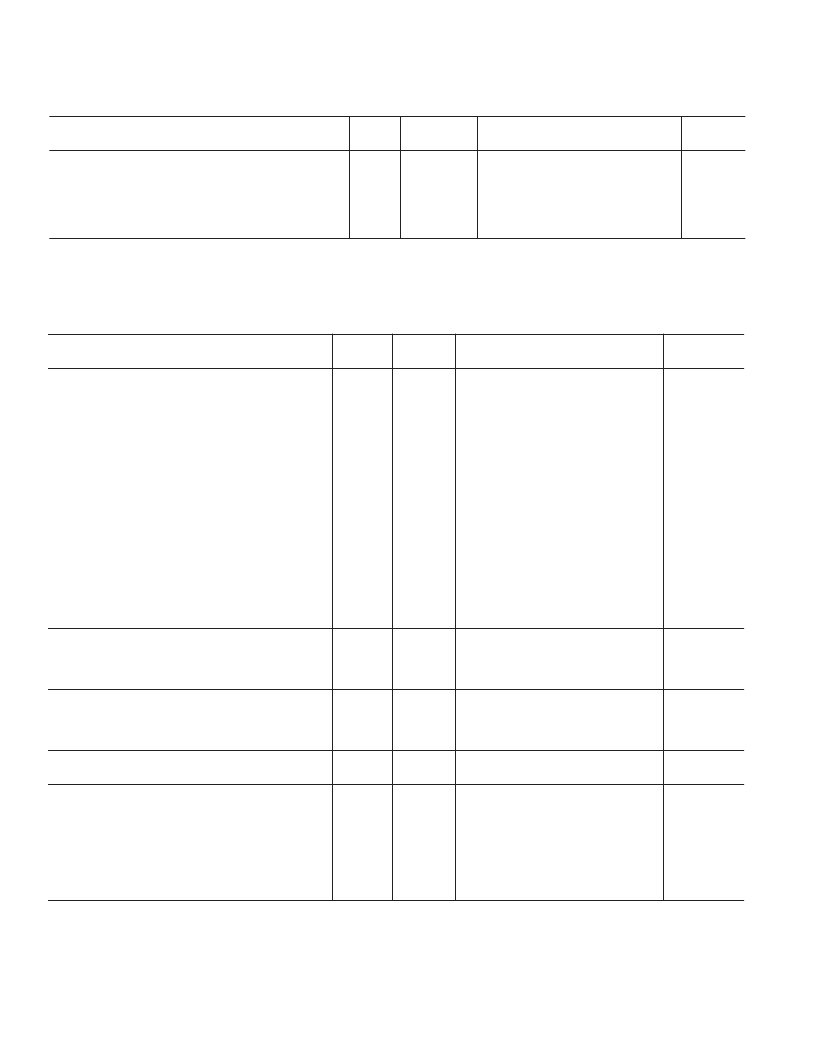

AD9860/AD9862

Test

Level

AD9860/AD9862

Typ

(20 pF Load)

Temp

Min

Max

Unit

Minimum Reset Pulsewidth Low (t

RL

)

Digital Output Rise/Fall Time

DLL Output Clock

DLL Output Duty Cycle

Tx

–

/Rx

–

Interface (See Figures 11 and 12)

TxSYNC/TxIQ Setup Time (t

Tx1

, t

Tx3

)

TxSYNC/TxIQ Hold Time (t

Tx2

, t

Tx4

)

RxSYNC/RxIQ/IF to Valid Time(t

Rx1

, t

Rx3

)

RxSYNC/RxIQ/IF Hold Time (t

Rx2

, t

Rx4

)

Serial Control Bus (See Figures 1 and 2)

Maximum SCLK Frequency (f

SCLK

)

Minimum Clock Pulsewidth High (t

HI

)

Minimum Clock Pulsewidth Low (t

LOW

)

Maximum Clock Rise/Fall Time

Minimum Data/SEN Setup Time (t

S

)

Minimum SEN/Data Hold Time (t

H

)

Minimum Data/SCLK Setup Time (t

DS

)

Minimum Data Hold Time (t

DH

)

Output Data Valid/SCLK Time (t

DV

)

NA

25

o

C

25

o

C

25

o

C

NA

III

III

III

5

2.8

32

Clock

Cycles

ns

MHz

%

4

128

50

25

o

C

25

o

C

25

o

C

25

o

C

III

III

III

III

3

3

ns

ns

ns

ns

5.2

0.2

Full

Full

Full

Full

Full

Full

Full

Full

Full

III

III

III

III

III

III

III

III

III

16

MHz

ns

ns

ms

ns

ns

ns

ns

ns

30

30

1

25

0

25

0

30

AUXILARY ADC

Conversion Rate

Input Range

Resolution

25

o

C

25

o

C

25

o

C

III

III

III

1.25

3

10

MHz

V

Bits

AUXILARY DAC

Settling Time

Output Range

Resolution

25

o

C

25

o

C

25

o

C

III

III

III

8

3

8

m

s

V

Bits

ADC TIMING

Latency (All Digital Processing Blocks Disabled)

25

o

C

III

7

Cycles

DAC Timing

Latency (All Digital Processing Blocks Disabled)

Latency (2 Interpolation Enabled)

Latency (4 Interpolation Enabled)

Additional Latency (Hilbert Filter Enabled)

Additional Latency (Coarse Modulation Enabled)

Additional Latency (Fine Modulation Enabled)

Output Settling Time (TST) (to 0.1%)

25

o

C

25

o

C

25

o

C

25

o

C

25

o

C

25

o

C

25

o

C

III

III

III

III

III

III

III

3

30

72

36

5

8

35

Cycles

Cycles

Cycles

Cycles

Cycles

Cycles

ns

Specifications subject to change without notice.

TIMING CHARACTERISTICS

Test

Level

AD9860/AD9862

Typ

PARAMETERS (continued)

Temp

Min

Max

Unit

POWER SUPPLY (continued)

Rx Path (f

ADC

= 64 MSPS)

Processing Blocks Disabled

Decimation Filter Enabled

Hilbert Filter Enabled

Hilbert and Decimation Filter Enabled

25

o

C

25

o

C

25

o

C

25

o

C

III

III

III

III

9

15

16

18.5

mA

mA

mA

mA

NOTES

1

% f

DATA

refers to the input data rate of the digital block.

2

Interpolation filter stop band is defined by image suppression of 50 dB or greater.

Specifications subject to change without notice.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9862 | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9862BST | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9864 | IF Digitizing Subsystem |

| AD9864-EB | IF Digitizing Subsystem |

| AD9864BCPZ | IF Digitizing Subsystem |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9861 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Mixed-Signal Front-End (MxFE⑩) Baseband Transceiver for Broadband Applications |

| AD9861-50EB | 制造商:Analog Devices 功能描述: |

| AD9861-50EBZ | 功能描述:BOARD EVALUATION FOR AD9861-50 RoHS:是 類別:RF/IF 和 RFID >> RF 評(píng)估和開發(fā)套件,板 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 類型:GPS 接收器 頻率:1575MHz 適用于相關(guān)產(chǎn)品:- 已供物品:模塊 其它名稱:SER3796 |

| AD9861-80EB | 制造商:Analog Devices 功能描述: |

| AD9861-80EBZ | 功能描述:BOARD EVALUATION FOR AD9861 RoHS:是 類別:RF/IF 和 RFID >> RF 評(píng)估和開發(fā)套件,板 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 類型:GPS 接收器 頻率:1575MHz 適用于相關(guān)產(chǎn)品:- 已供物品:模塊 其它名稱:SER3796 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。