- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9874BST (ANALOG DEVICES INC) IF Digitizing Subsystem PDF資料下載

參數資料

| 型號: | AD9874BST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網絡 |

| 英文描述: | IF Digitizing Subsystem |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP48 |

| 封裝: | PLASTIC, MS-026BBC, LQFP-48 |

| 文件頁數: | 2/40頁 |

| 文件大小: | 744K |

| 代理商: | AD9874BST |

第1頁當前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

REV. 0

–2–

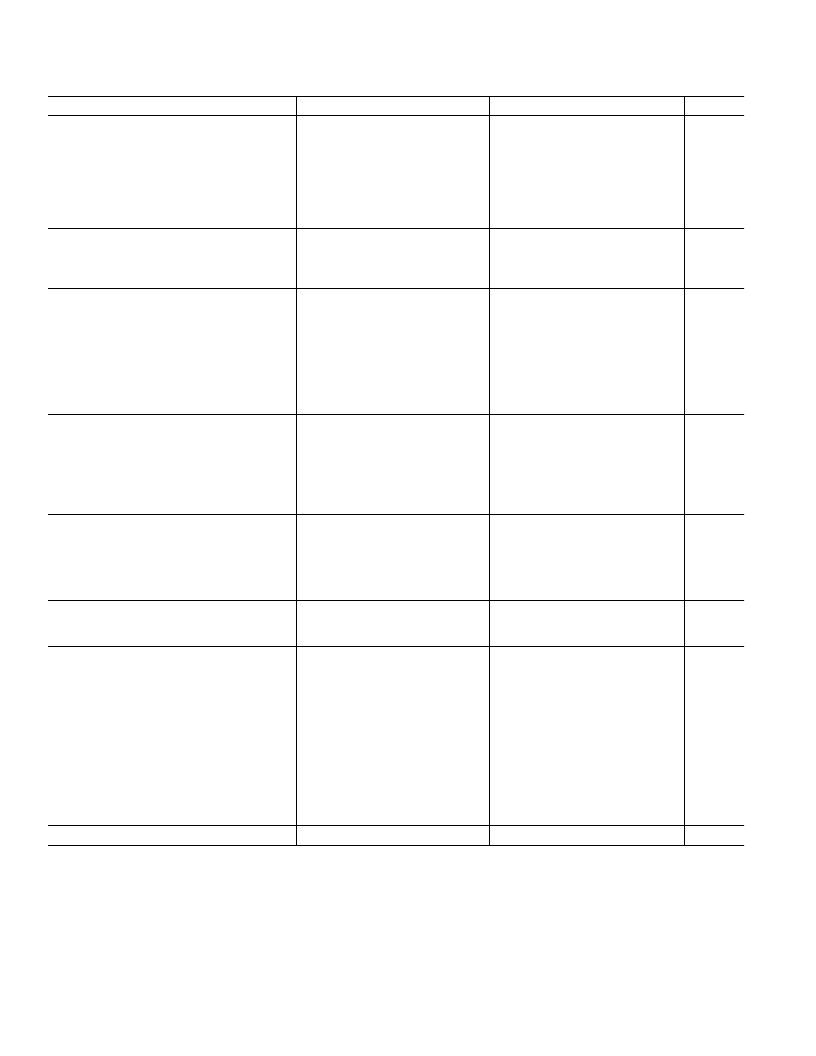

Parameter

Temp

Test Level

Min

Typ

Max

Unit

SYSTEM DYNAMIC PERFORMANCE

2

SSB Noise Figure @ Min VGA Attenuation

3,

4

@ Max VGA Attenuation

3, 4

Dynamic Range with AGC Enabled

3, 4

IF Input Clip Point @ Max VGA Attenuation

3

@ Min VGA Attenuation

3

Input Third Order Intercept (IIP3)

Gain Variation over Temperature

Full

Full

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

IV

IV

8.1

13

95

–19

–31

0

0.7

9.5

dB

dB

dB

dBm

dBm

dBm

dB

91

–20

–32

–5

2

LNA + MIXER

Maximum RF and LO Frequency Range

LNA Input Impedance

Mixer LO Input Resistance

Full

25

o

C

25

o

C

IV

V

V

300

500

370//1.4

1

MHz

//pF

k

LO SYNTHESIZER

LO Input Frequency

LO Input Amplitude

FREF (Reference) Frequency

FREF Input Amplitude

Minimum Charge Pump Current

@

5 V

5

Maximum Charge Pump Current

@

5 V

5

Charge Pump Output Compliance

6

Synthesizer Resolution

Full

Full

Full

Full

Full

Full

Full

Full

IV

IV

IV

IV

VI

VI

VI

IV

7.75

0.3

0.1

0.3

0.48

3.87

0.4

6.25

300

2.0

25

3

0.78

6.2

VDDP – 0.4

MHz

V p-p

MHz

V p-p

mA

mA

V

kHz

0.67

5.3

CLOCK SYNTHESIZER

CLK Input Frequency

CLK Input Amplitude

Minimum Charge Pump Output Current

5

Maximum Charge Pump Output Current

5

Charge Pump Output Compliance

6

Synthesizer Resolution

Full

Full

Full

Full

Full

Full

IV

IV

VI

VI

VI

IV

13

0.3

0.48

3.87

0.4

2.2

26

V

DDC

0.78

6.2

VDDQ – 0.4

MHz

V p-p

mA

mA

V

kHz

0.67

5.3

SIGMA-DELTA ADC

Resolution

Clock Frequency (f

CLK

)

Center Frequency

Pass-Band Gain Variation

Alias Attenuation

Full

Full

Full

Full

Full

IV

IV

V

IV

IV

16

13

24

26

Bits

MHz

MHz

dB

dB

f

CLK

/8

1.0

80

GAIN CONTROL

Programmable Gain Step

AGC Gain Range (Continuous)

Full

Full

V

V

16

12

dB

dB

OVERALL

Analog Supply Voltage

(VDDA, VDDF, VDDI)

Digital Supply Voltage

(VDDD, VDDC, VDDL)

Interface Supply Voltage

7

(VDDH)

Charge Pump Supply Voltage

(VDDP, VDDQ)

Total Current

High Performance Setting

8

Low Power Mode

8

Standby

Full

VI

2.7

3.0

3.6

V

Full

VI

2.7

3.0

3.6

V

Full

VI

1.8

3.6

V

Full

VI

2.7

5.0

5.5

V

Full

Full

Full

VI

VI

VI

20

17

0.01

26.5

22

0.1

mA

mA

mA

°

C

OPERATING TEMPERATURE RANGE

–40

+85

NOTES

1

Standard operating mode: LNA/Mixer @ high bias setting, VGA @ Min ATTEN setting, synthesizers in normal (not fast acquire) mode, f

CLK

= 18 MHz, decimation

factor = 900, 16-bit digital output, and 10 pF load on SSI output pins.

2

This includes 0.9 dB loss of matching network.

3

AGC with DVGA enabled.

4

Measured in 10 kHz bandwidth.

5

Programmable in 0.67 mA steps.

6

Voltage span in which LO (or CLK) charge pump output current is maintained within 5% of nominal value of VDDP/2 (or VDDQ/2).

7

VDDH must be less than VDDD + 0.5 V.

8

Clock VCO off, add additional 0.7 mA with VGA @ Max ATTEN setting.

Specifications subject to change without notice.

(VDDI = VDDF = VDDA = VDDC = VDDL = VDDD = VDDH = 2.7 to 3.6 V,

VDDQ = VDDP = 2.7 V to 5.5 V, f

CLK

= 18 MSPS, f

IF

= 109.65 MHz, f

LO

= 107.4 MHz, f

REF

= 16.8 MHz, unless otherwise noted.)

1

AD9874–SPECIFICATIONS

相關PDF資料 |

PDF描述 |

|---|---|

| AD9874EB | IF Digitizing Subsystem |

| AD9875BSTRL | Broadband Modem Mixed-Signal Front End |

| AD9875 | Broadband Modem Mixed-Signal Front End |

| AD9875-EB | Broadband Modem Mixed-Signal Front End |

| AD9875BST | Broadband Modem Mixed-Signal Front End |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9874EB | 制造商:AD 制造商全稱:Analog Devices 功能描述:IF Digitizing Subsystem |

| AD9874-EB | 制造商:Analog Devices 功能描述: |

| AD9874-EBZ | 功能描述:BOARD EVAL FOR AD9874 制造商:analog devices inc. 系列:- 零件狀態:有效 類型:數字轉換器 頻率:10MHz ~ 300MHz 配套使用產品/相關產品:AD9874 所含物品:板 標準包裝:1 |

| AD9875 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9875BST | 制造商:Analog Devices 功能描述:Modem Chip Single 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:10B BROADBAND MODEM MXFE CONVERTER - Tape and Reel |

發布緊急采購,3分鐘左右您將得到回復。