- 您現在的位置:買賣IC網 > PDF目錄373972 > AD9957BSVZ-REEL (ANALOG DEVICES INC) 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC PDF資料下載

參數資料

| 型號: | AD9957BSVZ-REEL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網絡 |

| 英文描述: | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP100 |

| 封裝: | ROHS COMPLIANT, MS-026AED-HD, TQFP-100 |

| 文件頁數: | 33/60頁 |

| 文件大小: | 840K |

| 代理商: | AD9957BSVZ-REEL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

AD9957

CLOCK INPUT (REF_CLK)

REFCLK OVERVIEW

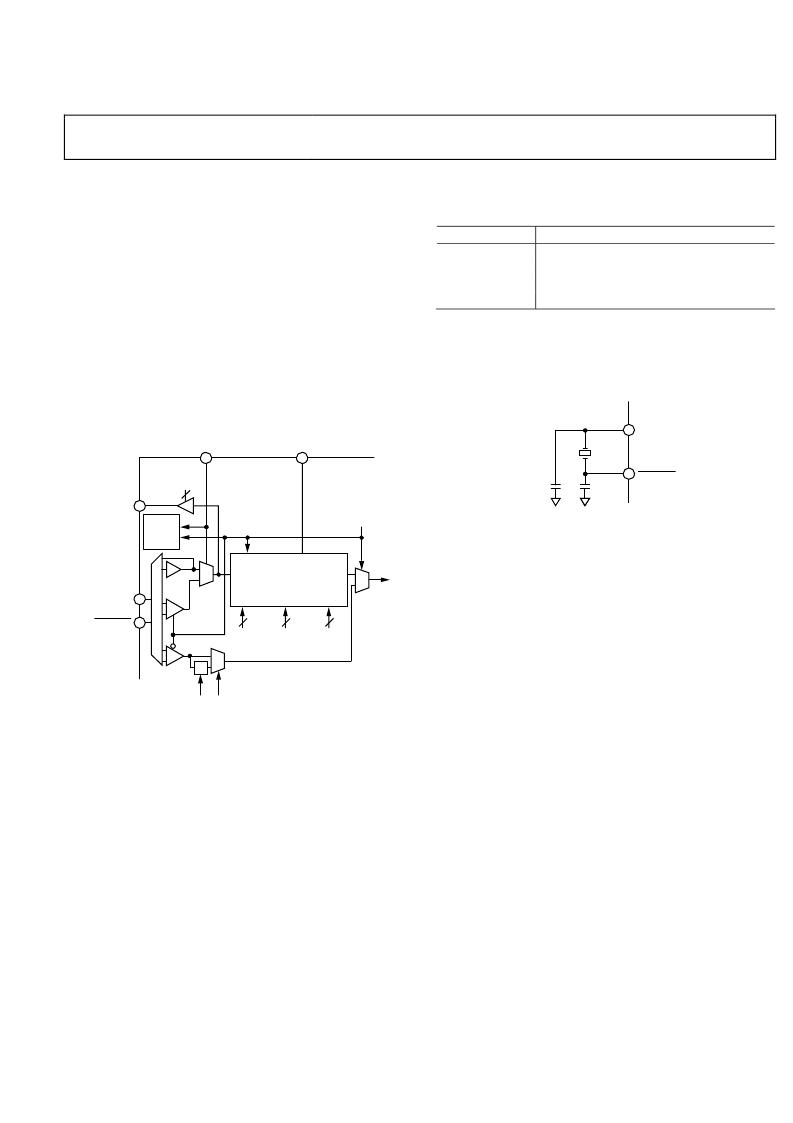

The AD9957 supports a number of options for producing the

internal SYSCLK signal (that is, the DAC sample clock) via the

REF_CLK input pins. The REF_CLK input can be driven

directly from a differential or single-ended source, or it can

accept a crystal connected across the two input pins. There is

also an internal phase-locked loop (PLL) multiplier that can be

independently enabled. A block diagram of the REF_CLK

functionality is shown in Figure 47. The various input configu-

rations are controlled by means of the XTAL_SEL pin and

control bits in the CFR3 register. Figure 47 also shows how the

CFR3 control bits are associated with specific functional blocks.

Rev. 0 | Page 33 of 60

REF_CLK

REF_CLK

PLL

VCO

SELECT

DIVIDE

CHARGE

PUMP

OUT

IN

PLL_LOOP_FILTER

ENABLE

PLL_LOOP_FILTER

DRV

CFR3

<31:30>

2

REFCLK_OUT

XTAL_SEL

REFCLK

INPUT

SELECT

LOGIC

SYSCLK

ICP

CFR3

<21:19>

N

CFR3

<7:1>

VCO

CFR3

<26:24>

÷2

INPUT DIVIDER BYPASS

CFR3<15>

PLL_ENABLE

CFR3

<8>

INPUT DIVIDER

RESET

CFR3<14>

Figure 47. REF_CLK Block Diagram

94

95

2

90

91

0

1

0

1

2

7

3

0

1

0

The PLL enable bit is used to choose between the PLL path or

the direct input path. When the direct input path is selected, the

REF_CLK pins must be driven by an external signal source

(single-ended or differential). Input frequencies up to 2 GHz are

supported. For input frequencies greater than 1 GHz, the input

divider must be enabled for proper operation of the device.

When the PLL is enabled, a buffered clock signal is available at

the REFCLK_OUT pin. This clock signal is the same frequency

as the REF_CLK input. This is especially useful when a crystal

is connected, because it gives the user a replica of the crystal

clock for driving other external devices. The REFCLK_OUT

buffer is controlled by two bits as listed in Table 7.

Table 7. REFCLK_OUT Buffer Control

CFR3<31:30>

REFCLK_OUT Buffer

00

Disabled

01

Low output current

10

Medium output current

11

High output current

CRYSTAL DRIVEN REF_CLK

When using a crystal at the REF_CLK input, the resonant

frequency should be approximately 25 MHz. Figure 48 shows

the recommended circuit configuration.

0

REF_CLK

REF_CLK

39pF

39pF

XTAL

90

91

Figure 48. Crystal Connection Diagram

DIRECT DRIVEN REF_CLK

When driving the REF_CLK inputs directly from a signal

source, either single-ended or differential signals can be used.

With a differential signal source, the REF_CLK pins are driven

with complementary signals and ac-coupled with 0.1 μF

capacitors. With a single-ended signal source, either a single-

ended-to-differential conversion can be employed or the

REF_CLK input can be driven single-ended directly. In either

case, 0.1 μF capacitors are used to ac couple both REF_CLK

pins to avoid disturbing the internal dc bias voltage of ~1.35 V.

See Figure 49 for more details.

The REF_CLK input resistance is ~2.5 kΩ differential (~1.2 kΩ

single-ended). Most signal sources have relatively low output

impedances. The REF_CLK input resistance is relatively high,

therefore, its effect on the termination impedance is negligible

and can usually be chosen to be the same as the output imped-

ance of the signal source. The bottom two examples in Figure 49

assume a signal source with a 50 Ω output impedance.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9957_07 | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9958BCPZ-REEL7 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958BCPZ | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9970 | 14-Bit CCD Signal Processor with Precision Timing Generator |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9957BSVZREEL13 | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Quadrature Digital Upconverter w/18-Bit IQ Data Path and 14-Bit DAC |

| AD9958 | 制造商:AD 制造商全稱:Analog Devices 功能描述:2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958 PCB | 制造商:Analog Devices 功能描述:EVAL BOARD ((NS)) |

| AD9958/PCB | 制造商:Analog Devices 功能描述:Evaluation Board For 2-Channel 500 MSPS DDS With 10-Bit DACs 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:IC 10-BIT DAC DDS |

| AD9958/PCBZ | 功能描述:BOARD EVALUATION FOR AD9958 RoHS:是 類別:編程器,開發系統 >> 評估演示板和套件 系列:AgileRF™ 標準包裝:1 系列:PSoC® 主要目的:電源管理,熱管理 嵌入式:- 已用 IC / 零件:- 主要屬性:- 次要屬性:- 已供物品:板,CD,電源 |

發布緊急采購,3分鐘左右您將得到回復。