- 您現在的位置:買賣IC網 > PDF目錄373972 > AD9957BSVZ-REEL (ANALOG DEVICES INC) 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC PDF資料下載

參數資料

| 型號: | AD9957BSVZ-REEL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網絡 |

| 英文描述: | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP100 |

| 封裝: | ROHS COMPLIANT, MS-026AED-HD, TQFP-100 |

| 文件頁數: | 37/60頁 |

| 文件大小: | 840K |

| 代理商: | AD9957BSVZ-REEL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

AD9957

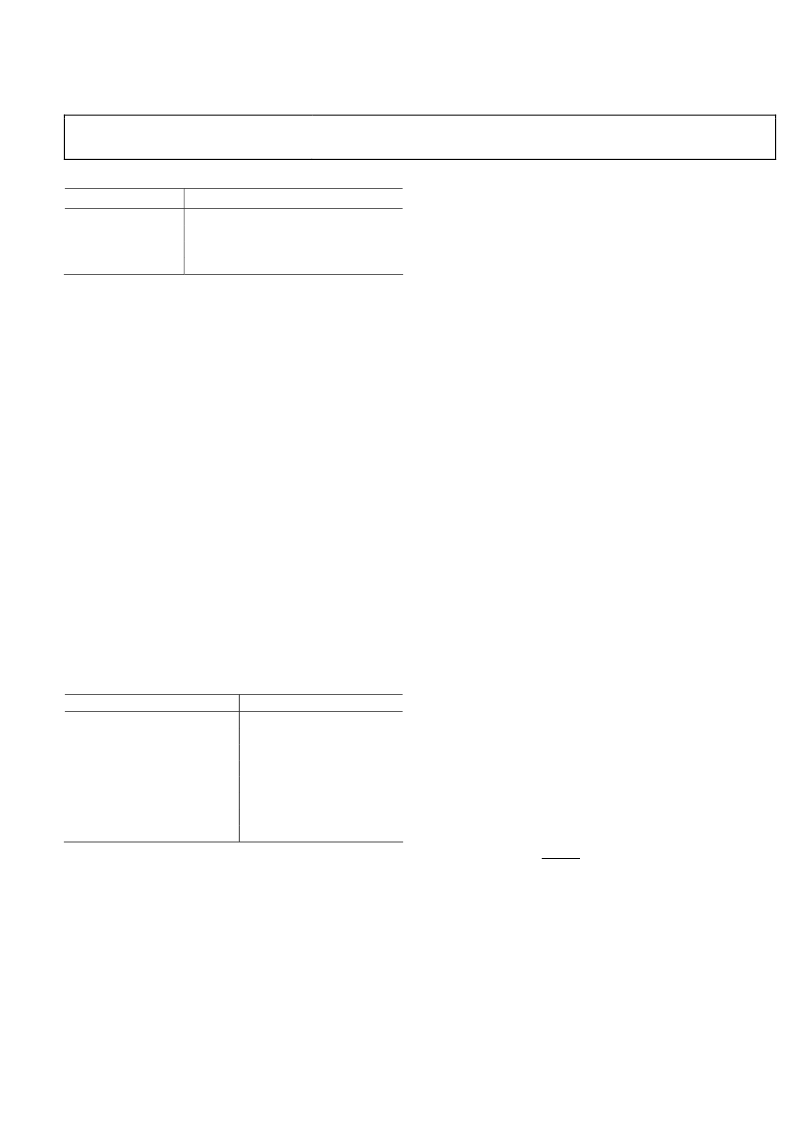

Table 10. OSK Amplitude Step Size

ASF<1:0>

00

01

10

11

Rev. 0 | Page 37 of 60

Amplitude Step Size

1

2

4

8

As mentioned earlier, the step interval is controlled by a 16-bit

programmable timer. Normally, this timer is loaded with the

programmed timing value whenever the timer expires, thus

initiating a new timing cycle. However, three events cause the

timer to have its timing value reloaded prior to the timer

expiring. One such event is when the select auto-OSK bit is

transitioned from a Logic 0 state to a Logic 1 state followed by

an I/O update. A second such event is a change of state in the

OSK pin. The third event is dependent on the status of the Load

ARR @ I/O Update bit. If this bit is Logic 0, then no action occurs,

otherwise, when the I/O_UPDATE pin is asserted (or a profile

change occurs), the timer resets to its initial starting point.

PROFILES

Each of the three operating modes of the AD9957 support the

use of profiles, which consist of a group of registers containing

pertinent operating parameters for a particular operating mode.

Profiles enable rapid switching between parameter sets. Profile

parameters are programmed via the serial I/O port. Once

programmed, a specific profile is activated by means of three

external pins (PROFILE<2:0>). A particular profile is activated

by providing the appropriate logic levels to the profile control

pins per the settings listed in Table 11.

Table 11. Profile Control Pins

PROFILE<2:0>

000

001

010

011

100

101

110

111

Active Profile

0

1

2

3

4

5

6

7

Consider an application of basic two-tone frequency shift

keying (FSK) where binary data is transmitted by selecting

between two different frequencies: a mark frequency (Logic 1)

and a space frequency (Logic 0). To accommodate FSK, the

Profile 0 register is programmed with the appropriate frequency

tuning word for a space, and the Profile 1 register is programmed

with the appropriate frequency tuning word for a mark. Then,

with the PROFILE1 and PROFILE2 pins tied to Logic 0, the

PROFILE0 pin is used to transmit the data bits. The logic state

of the PROFILE0 pin causes the appropriate mark and space

frequencies to be generated.

I/O_UPDATE PIN

By default, the I/O_UPDATE pin is an input that serves as a

strobe signal to allow synchronous update of the device operating

parameters. For example, frequency, phase, and amplitude con-

trol words for the DDS can be programmed using the serial I/O

port. However, the serial I/O port is an asynchronous interface;

consequently, programming of the device operating parameters

using the I/O port is not synchronized with the internal timing.

Using the pin, I/O_UPDATE, the user can synchronize the

application of certain programmed operating parameters with

external circuitry when new parameters are programmed into

the I/O registers. A rising edge on I/O_UPDATE initiates transfer

of the register contents to the internal workings of the device.

The transfer of programmed data from the programming

registers to the internal hardware is also accomplished by

changing the state of the profile pins.

AUTOMATIC I/O UPDATE

The AD9957 offers an option whereby the I/O update function

is asserted automatically rather than relying on an external

signal supplied by the user. This feature is enabled by setting the

internal I/O update active bit in CFR2.

When this feature is active, the I/O_UPDATE pin becomes an

output pin. It generates an active high pulse each time an inter-

nal I/O update occurs. The duration of the pulse is approximately

12 cycles of SYSCLK. This I/O update strobe can be used to

notify an external controller that the device has generated an

I/O update internally.

The repetition rate of the internal I/O update is programmed

via the serial I/O port. Two parameters control the repetition

rate. The first parameter consists of the two I/O update rate

control bits in CFR2. The second parameter is the 32-bit word

in the I/O update rate register that sets the range of an internal

counter.

The I/O update rate control bits establish a divide by 1, 2, 4, or 8

of a clock signal that runs at f

SYSCLK

. The output of the divider

clocks the aforementioned 32-bit internal counter. The repetition

rate of the I/O update is given by

B

f

f

A

SYSCLK

2

UPDATE

O

I

_

/

=

where:

A

is the value of the 2-bit word comprising the I/O update rate

control bits. The default value of A is 0.

B

is the value of the 32-bit word stored in the I/O update rate

register. The default value of B is 0xFFFF.

If B is programmed to 0x0003 or less, the I/O_UPDATE pin no

longer pulses, but assumes a static Logic 1 state.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9957_07 | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9958BCPZ-REEL7 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958BCPZ | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9970 | 14-Bit CCD Signal Processor with Precision Timing Generator |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9957BSVZREEL13 | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Quadrature Digital Upconverter w/18-Bit IQ Data Path and 14-Bit DAC |

| AD9958 | 制造商:AD 制造商全稱:Analog Devices 功能描述:2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958 PCB | 制造商:Analog Devices 功能描述:EVAL BOARD ((NS)) |

| AD9958/PCB | 制造商:Analog Devices 功能描述:Evaluation Board For 2-Channel 500 MSPS DDS With 10-Bit DACs 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:IC 10-BIT DAC DDS |

| AD9958/PCBZ | 功能描述:BOARD EVALUATION FOR AD9958 RoHS:是 類別:編程器,開發系統 >> 評估演示板和套件 系列:AgileRF™ 標準包裝:1 系列:PSoC® 主要目的:電源管理,熱管理 嵌入式:- 已用 IC / 零件:- 主要屬性:- 次要屬性:- 已供物品:板,CD,電源 |

發布緊急采購,3分鐘左右您將得到回復。