- 您現在的位置:買賣IC網 > PDF目錄374044 > ADV601 (Analog Devices, Inc.) Low Cost Multiformat Video Codec PDF資料下載

參數資料

| 型號: | ADV601 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 視頻Codec |

| 英文描述: | Low Cost Multiformat Video Codec |

| 中文描述: | 低成本多格式視頻解碼器 |

| 文件頁數: | 47/52頁 |

| 文件大小: | 606K |

| 代理商: | ADV601 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁當前第47頁第48頁第49頁第50頁第51頁第52頁

ADV601

–47–

REV. 0

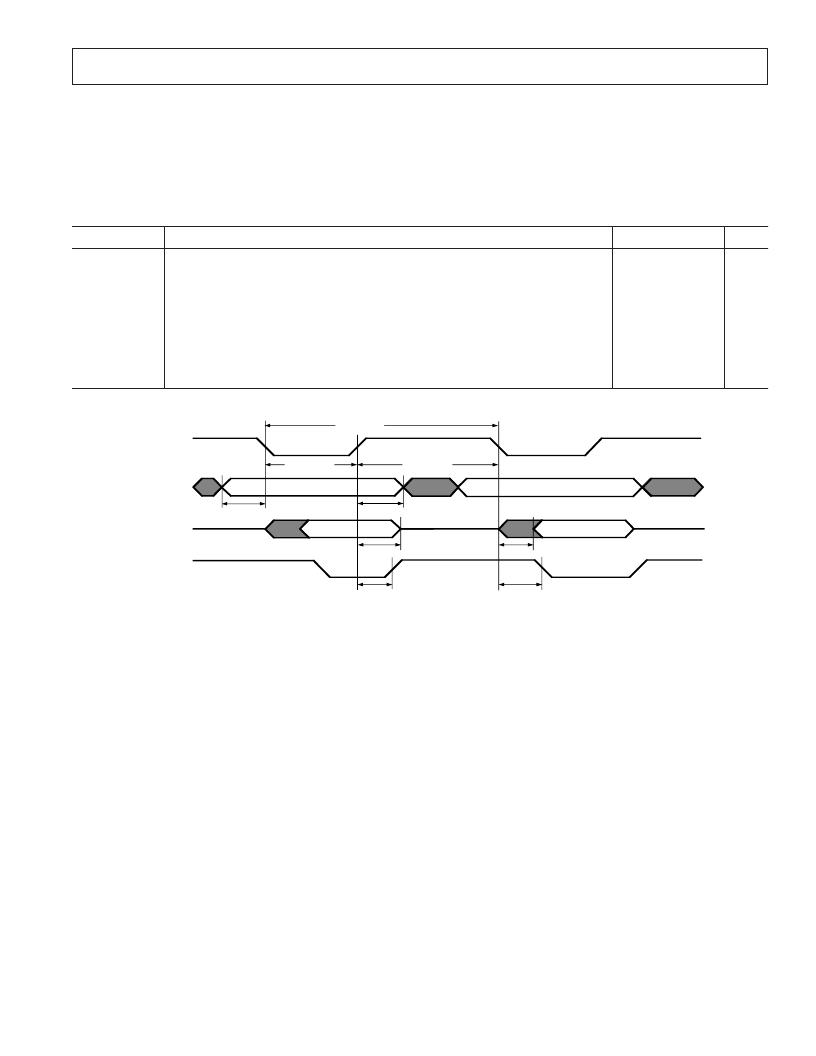

Host Interface (Compressed Data) Register Timing

The diagrams in this section show transfer timing for host read and write transfers to the ADV601’s Compressed Data register. Ac-

cesses to the Compressed Data register are faster than access timing for the Indirect Address, Indirect Register Data, and Interrupt

Mask/Status registers. For information on access timing for the other registers, see the Host Interface (Indirect Address

,

Indirect

Regis

ter Data, and Interrupt Mask/Status) Register Timing section. Also note that as long as your system observes the

RD

or

WR

signal assertion timing, your system does

NOT

have to wait for the

ACK

signal between new compressed data addresses.

Table XXXV. Host (Compressed Data) Read Timing Parameters

Parameter

Description

Min

Max

Unit

t

RD_CD_RDC

t

RD_CD_PWA

t

RD_CD_PWD

t

ADR_CD_RDS

t

ADR_CD_RDH

t

DATA_CD_RDD

t

DATA_CD_RDOH

t

ACK_CD_RDD

t

ACK_CD_RDOH

RD

Signal, Compressed Data Direct Register, Read Cycle Time

RD

Signal, Compressed Data Direct Register, Pulse Width Asserted

RD

Signal, Compressed Data Direct Register, Pulse Width Deasserted

ADR Bus, Compressed Data Direct Register, Read Setup

ADR Bus, Compressed Data Direct Register, Read Hold (at 27 MHz VCLK)

DATA Bus, Compressed Data Direct Register, Read Delay

DATA Bus, Compressed Data Direct Register, Read Output Hold

ACK

Signal, Compressed Data Direct Register, Read Delay

ACK

Signal, Compressed Data Direct Register, Read Output Hold

28

10

10

2

2

N/A

18

N/A

9

N/A

N/A

N/A

N/A

N/A

10

N/A

18

N/A

ns

ns

ns

ns

ns

ns

ns

ns

ns

(I) ADR,

BE

,

CS

(I)

RD

(O) DATA

(O)

ACK

VALID

VALID

VALID

VALID

t

ADR_CD_RDS

t

DATA_CD_RDD

t

ACK_CD_RDD

t

ACK_CD_RDOH

t

DATA_CD_RDOH

t

ADR_CD_RDH

t

RD_CD_RDC

t

RD_CD_PWA

t

RD_CD_PWD

Figure 39. Host (Compressed Data) Read Transfer Timing

相關PDF資料 |

PDF描述 |

|---|---|

| ADV601JS | Low Cost Multiformat Video Codec |

| ADV601LC | Ultralow Cost Video Codec |

| ADV601LCJST | Ultralow Cost Video Codec |

| ADV7120KP30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120 | CMOS 80 MHz, Triple 8-Bit Video DAC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV601E-VIDEOPIPE | 制造商:Analog Devices 功能描述:VIDEOPIPE |

| ADV601JS | 制造商:Analog Devices 功能描述:Multiformat Video Codec 160-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADV601JS12 | 制造商:Analog Devices 功能描述:Multiformat Video Codec 160-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:DIGITAL VIDEO CODEC REV 1.2 - Bulk |

| ADV601LC | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Cost Video Codec |

| ADV601LCERAG1266B-0.5 | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。