- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375789 > FEDL7204-001DIGEST-01 (OKI SEMICONDUCTOR CO., LTD.) The ML7204-001 is a speech CODEC for VoIP. PDF資料下載

參數(shù)資料

| 型號: | FEDL7204-001DIGEST-01 |

| 廠商: | OKI SEMICONDUCTOR CO., LTD. |

| 元件分類: | Codec |

| 英文描述: | The ML7204-001 is a speech CODEC for VoIP. |

| 中文描述: | 在ML7204 - 001是一種VoIP語音編解碼器。 |

| 文件頁數(shù): | 10/42頁 |

| 文件大小: | 792K |

| 代理商: | FEDL7204-001DIGEST-01 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

FEDL7204-001DIGEST-01

OKI Semiconductor

ML7204-001

10/42

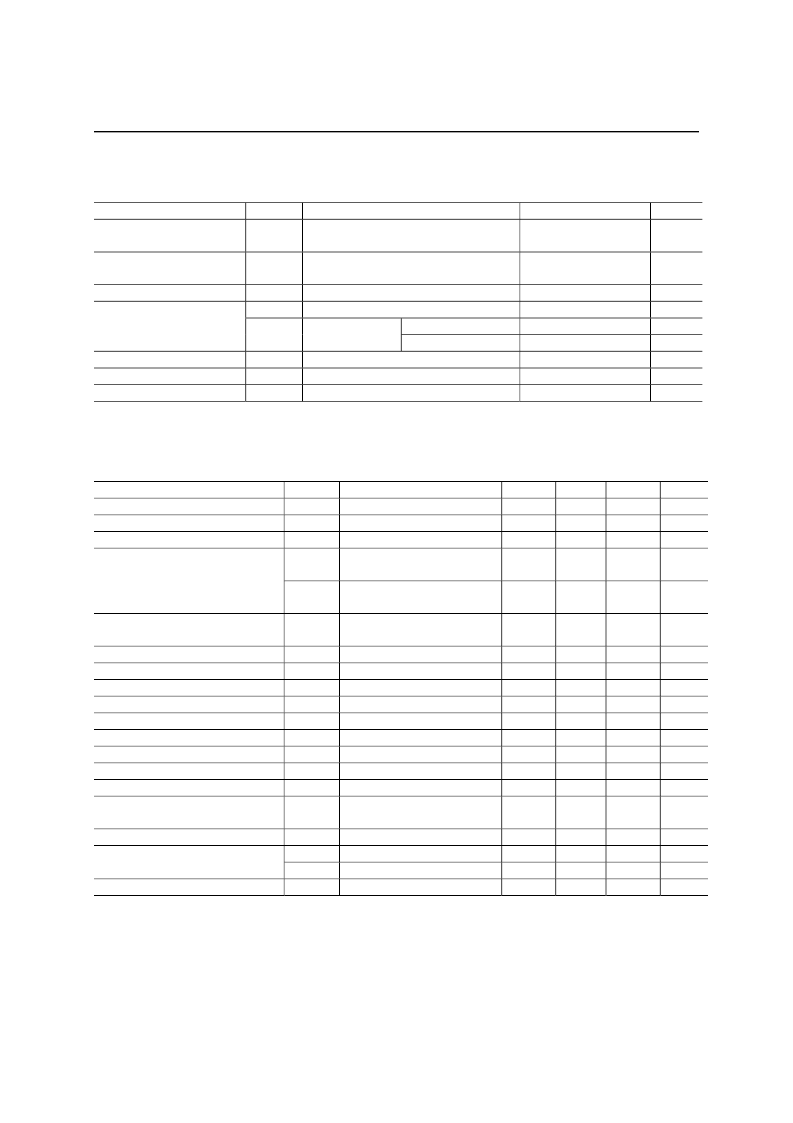

ABSOLUTE MAXIMUM RATINGS

Parameter

Analog power supply

voltage

Digital power supply

voltage

Analog input voltage

Symbol

Condition

Rating

Unit

AVDD

—

–0.3 to +4.6

V

DVDD

—

–0.3 to +4.6

V

VAIN

VDIN1

Analog pin

Normal digital pin

DVDD = 3.0 to 3.6 V

5 V tolerant pin

–0.3 to AVDD+0.3

–0.3 to DVDD+0.3

–0.3 to +6.0

–0.3 to DVDD+0.3

–20 to +20

350

–65 to +150

V

V

V

V

mA

mW

°

C

Digital input voltage

VDIN2

DVDD < 3.0 V

Output current

Power dissipation

Storage temperature

IO

PD

Tstg

—

Ta = 60

°

C, per package

—

RECOMMENDED OPERATING CONDITIONS

(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2

= 0.0 V, Ta = –20 to 60

°

C unless otherwise specified)

Symbol

Condition

AVDD

—

DVDD

—

Ta

—

Parameter

Min.

3.0

3.0

–20

0.75

×

DVDD

0.75

×

DVDD

Typ.

3.3

3.3

—

Max.

3.6

3.6

60

DVDD+

0.3

Unit

V

V

°

C

Analog power supply voltage

Digital power supply voltage

Operating temperature range

VIH1

Normal digital pin

—

V

Digital high-level input voltage

VIH2

5 V tolerant pin

—

5.5

V

Digital low-level input voltage

VIL

Digital pin

–0.3

—

0.19

×

DVDD

20

20

50

—

4.7+0.1

—

—

V

Digital input rise time

Digital input fall time

Digital output load capacitance

Digital output load resistance

AVREF bypass capacitor

VREGOUT bypass capacitor

VBG bypass capacitor

Master clock frequency

PCM shift clock frequency

PCM synchronous signal

frequency

Clock duty ratio

tIR

tIF

CDL

RDL

Cvref

Cvout

CVBG

Fmck

Fbclk

Digital pin

Digital pin

Digital pin

—

—

—

500

2.2+0.1

—

—

–0.01%

64

2

2

—

—

—

ns

ns

pF

μ

F

μ

F

pF

MHz

kHz

Pull-up resistance, PCMO

Between AVREF-AGND

Between VREGOUT-DGND

Between VBG-DGND

MCK

BCLK (at input)

10+0.1

150

12.288 +0.01%

—

2048

Fsync

SYNC (at input)

—

8.0

—

kHz

DRCLK

tBS

tSB

tWS

MCK, BCLK (at input)

BCLK to SYNC (at input)

SYNC to BCLK (at input)

SYNC (at input)

40

100

100

1BCLK

50

—

—

—

60

—

—

100

%

ns

ns

μ

s

PCM synchronous timing

PCM synchronous signal width

(Note) On power-on/shut-down sequence

For the analog power supply voltage (AVDD) and the digital power supply voltage (DVDD) to be supplied to

this LSI, it is recommended that power be applied to them simultaneously. However, if simultaneous power-up

is difficult due to the power supply circuit configuration, power them up in the order of DVDD

→

AVDD.

The power supplies should be shut down in the reverse order of power-on sequence.

相關PDF資料 |

PDF描述 |

|---|---|

| FEDS81V26000-01 | 1,114,112-Word X 24-Bit Field Memory |

| FEDS82V16520A-01 | 262,144-Word 】 32-Bit 】 2-Bank SGRAM |

| FEDS82V48540-01 | 393,216-Word 】 32-Bit 】 4-Bank FIFO-SGRAM |

| FEP16AT | Fast Rectifiers (Glass Passivated) |

| FEP16DT | DIODE SM SCHOT C-2PF SOT-23 SINGLE |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| FEDM08P1001 | 制造商:Baumer Electric 功能描述:Through Beam Sensors 3-Pin |

| FEDM10TPN0416A075 | 制造商:SOURIAU 功能描述:PLUG 10TP 4CTS |

| FEDM10TPN04-16A090 | 制造商:SOURIAU 功能描述:PLUG 10TP 4CTS |

| FEDM10TPN0416A100/TP2FD20MDA20 | 制造商:SOURIAU 功能描述:FEDM10TPN0416A100/TP2FD20MDA20 |

| FEDM10TPN0720A070 | 制造商:SOURIAU 功能描述:PLUG 10TP 7CTS |

發(fā)布緊急采購,3分鐘左右您將得到回復。