- 您現在的位置:買賣IC網 > PDF目錄376314 > RM7000-266T (PMC-SIERRA INC) RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released PDF資料下載

參數資料

| 型號: | RM7000-266T |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| 中文描述: | 64-BIT, 266 MHz, RISC PROCESSOR, PBGA304 |

| 封裝: | 31 X 31 MM, TBGA-304 |

| 文件頁數: | 37/54頁 |

| 文件大小: | 901K |

| 代理商: | RM7000-266T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer

’

s Internal Use

Document ID: PMC-2002175, Issue 1

37

RM7000

Microprocessor with On-Chip Secondary Cache Datasheet

Released

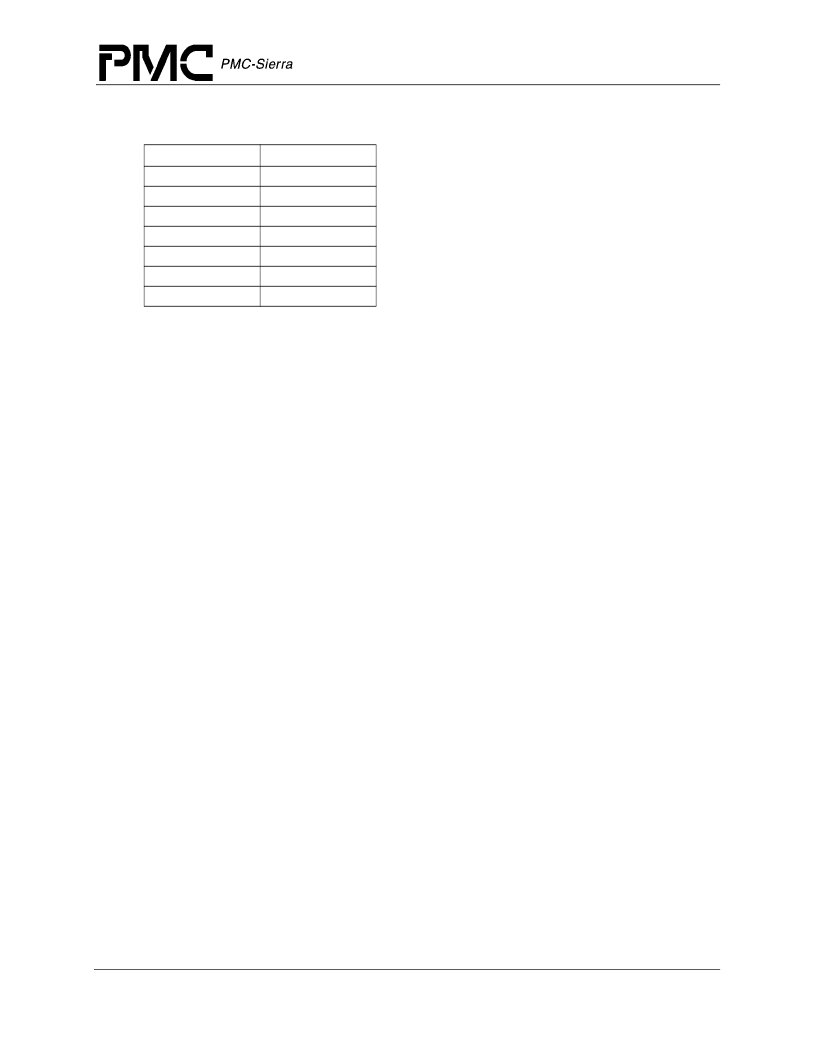

Table 15 Interrupt Vector Spacing

ICR[4..0]

0x0

0x1

0x2

0x4

0x8

0x10

others

4.36 Standby Mode

The RM7000 provides a means to reduce the amount of power consumed by the internal core

when the CPU would not otherwise be performing any useful operations. This state is known as

Standby Mode.

Executing the

WAIT

instruction enables interrupts and enters Standby Mode. When the

WAIT

instruction completes the W pipe stage, if the

SysAD

bus is currently idle, the internal processor

clocks will stop thereby freezing the pipeline. The phase lock loop, or PLL, internal timer/counter,

and the

“

wake up

”

input pins:

INT[9:0]*

,

NMI*

,

ExtReq*

,

Reset*

, and

ColdReset*

continue to

operate in their normal fashion. If the

SysAD

bus is not idle when the WAIT instruction completes

the W pipe stage, then the

WAIT

is treated as a

NOP

. Once the processor is in Standby, any

interrupt, including the internally generated timer interrupt, will cause the processor to exit

Standby and resume operation where it left off. The

WAIT

instruction is typically inserted in the

idle loop of the operating system or real time executive.

4.37 JTAG Interface

The RM7000 interface supports JTAG boundary scan in conformance with IEEE 1149.1. The

JTAG interface is especially helpful for checking the integrity of the processor

’

s pin connections.

4.38 Boot-Time Options

Fundamental operational modes for the processor are initialized by the boot-time mode control

interface. The boot-time mode control interface is a serial interface operating at a very low

frequency (SysClock divided by 256). The low frequency operation allows the initialization

information to be kept in a low cost EPROM; alternatively the twenty or so bits could be generated

by the system interface ASIC.

Immediately after the

VccOK

signal is asserted, the processor reads a serial bit stream of 256 bits

to initialize all the fundamental operational modes. ModeClock runs continuously from the

assertion of

VccOK

.

4.39 Boot-Time Modes

The boot-time serial mode stream is defined in Table 16. Bit 0 is the bit presented to the processor

when

VccOK

is de-asserted; bit 255 is the last.

Spacing

0x000

0x020

0x040

0x080

0x100

0x200

reserved

相關PDF資料 |

PDF描述 |

|---|---|

| RM7000-300S | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7000-300T | RM7000⑩ Microprocessor with On-Chip Secondary Cache Datasheet Released |

| RM7935 | 64-bit Microprocessors with Integrated L2 Cache and EJTAG |

| RM7965 | 64-bit Microprocessors with Integrated L2 Cache and EJTAG |

| RMLA3565-58 | Wideband Low Noise MMIC Amplifier |

相關代理商/技術參數 |

參數描述 |

|---|---|

| RM7000-300T | 制造商:QED 功能描述: 制造商:QED 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA |

| RM7000A | 制造商:PMC 制造商全稱:PMC 功能描述:64-Bit MIPS RISC Microprocessor with Integrated L2 Cache |

| RM7000A-300T | 制造商:Quantum Effect Devices 功能描述:64-BIT, 300 MHz, MICROPROCESSOR, 304 Pin Plastic BGA |

| RM7000A-350T | 制造商:PMC-Sierra 功能描述:Microprocessor, 64 Bit, 304 Pin, Plastic, BGA |

發布緊急采購,3分鐘左右您將得到回復。