- 您現在的位置:買賣IC網 > PDF目錄98301 > TSC2008TRGVRQ1 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQCC16 PDF資料下載

參數資料

| 型號: | TSC2008TRGVRQ1 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

| 封裝: | 4 X 4 MM, PLASTIC, VQFN-16 |

| 文件頁數: | 21/35頁 |

| 文件大小: | 418K |

| 代理商: | TSC2008TRGVRQ1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

SBAS552

– JUNE 2011

12-Bit Operation

For 12-bit operation, sending the conversion result across the SPI bus takes 16 or 24 bus clocks (SCLK clock);

see Figure 32 and Figure 31. There is an additional SCLK to be added to accommodate the cycle overhead (time

between consecutive cycles) so that the total bus cycle time used for calculating the throughput is actually 17 or

25 bus clocks (SCLK clock), respectively. Using a TSC2046-compatible SDO output mode or an SDO-adjusted

output mode does not affect the transmission time.

Seven sample-and-conversions take (19 x 7) internal clocks to complete. The MAV filter loop requires 19 internal

clocks. For VDD = 1.2V, the complete processed data cycle time calculations are shown in Table 6. Because the

first acquisition cycle overlaps with the I/O cycle, four CCLKs must be deducted from the total CCLK cycles. The

total time required is (19

× 7 + 19) – 4 = 148 CCLKs plus I/O.

8-Bit Operation

For 8-bit operation, sending the conversion result across the SPI bus takes 8, 16, or 24 bus clocks (SCLK clock);

see Figure 34, Figure 33, and Figure 31. There is an additional SCLK to be added to accommodate the cycle

overhead (time between consecutive cycles) so that the total bus cycle time used for calculating the throughput is

actually 9, 17, or 25 bus clocks (SCLK clock), respectively. Sending the conversion result takes 17 or 25 SCLKs

using 8-bit resolution and a TSC2046-compatible SDO output mode. If an SDO-adjusted output mode is used

with 8-bit resolution, it takes only 9 or 17 SCLKs to send the result back to host.

Seven sample-and-conversions take (16 x 7) internal clocks to complete. The MAV filter loop takes 19 internal

clocks. For VDD = 1.2V, the complete processed data cycle time calculations are shown in Table 6. Because the

first acquisition cycle is overlapped with the I/O cycle, four CCLKs must be deducted from the total CCLK cycles.

The total time required is (16

× 7 + 19) – 4 = 127 CCLKs plus I/O.

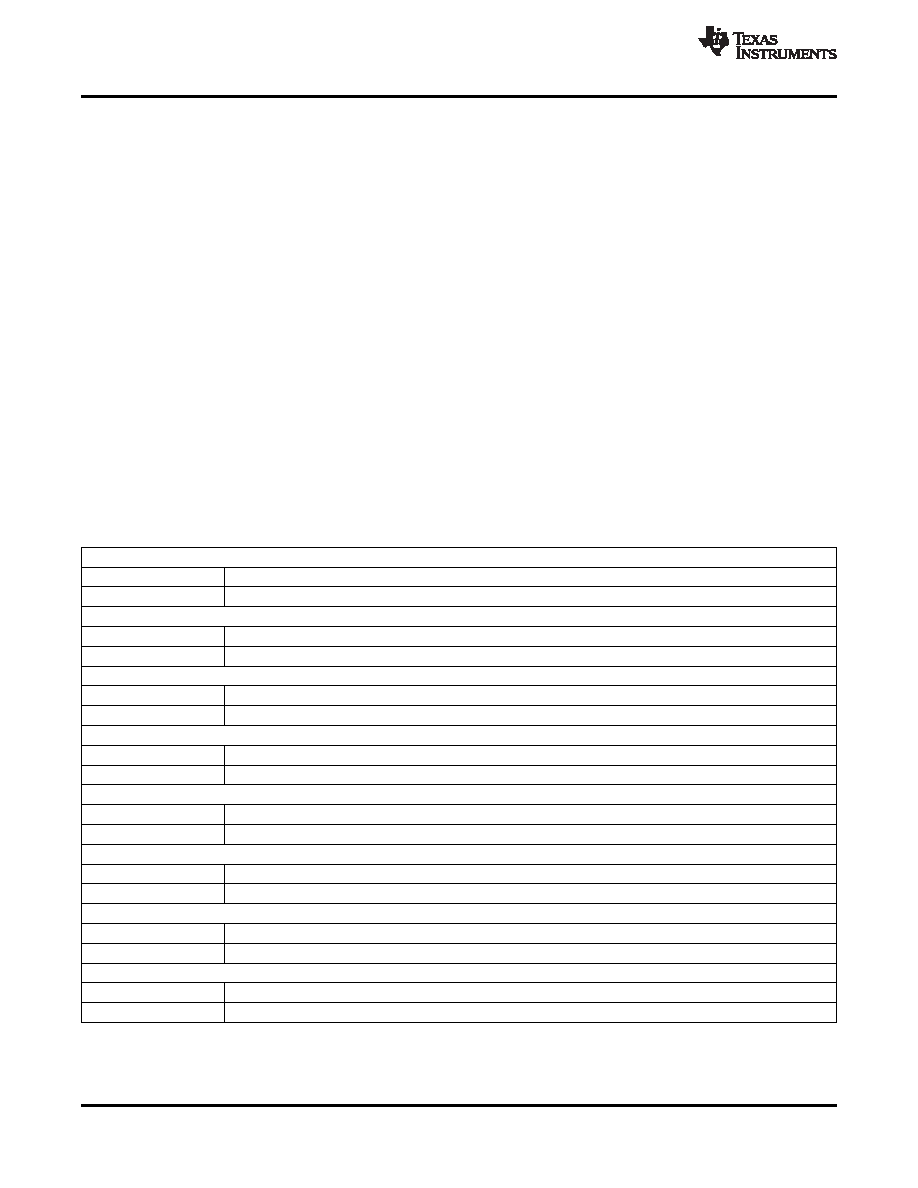

Table 6. Measurement Cycle Time Calculations(1) (2)

fSCLK = 100kHz (Period = 10μs)

8-Bit

17

× 10μs + 127 × 322.6ns = 211.0μs

12-Bit

25

× 10μs + 148 × 645.2ns = 345.5μs

fSCLK = 1MHz (Period = 1μs)

8-Bit

17

× 1μs + 127 × 322.6ns = 58.0μs

12-Bit

25

× 1μs + 148 × 645.2ns = 120.5μs

fSCLK = 2MHz (Period = 500ns)

8-Bit

17

× 500ns + 127 × 322.6ns = 49.5μs

12-Bit

25

× 500ns + 148 × 645.2ns = 108.0μs

fSCLK = 2.5MHz (Period = 400ns)

8-Bit

17

× 400ns + 127 × 322.6ns = 47.8μs

12-Bit

25

× 400ns + 148 × 645.2ns = 105.5μs

fSCLK = 4MHz (Period = 250ns)

8-Bit

17

× 250ns + 127 × 322.6ns = 45.2μs

12-Bit

25

× 250ns + 148 × 645.2ns = 101.7μs

fSCLK = 10MHz (Period = 100ns)

8-Bit

17

× 100ns + 127 × 322.6ns = 42.7μs

12-Bit

25

× 100ns + 148 × 645.2ns = 98.0μs

fSCLK = 16MHz (Period = 62.5ns)

8-Bit

17

× 62.5ns + 127 × 322.6ns = 42.0μs

12-Bit

25

× 62.5ns + 148 × 645.2ns = 97.1μs

fSCLK = 25MHz (Period = 40ns)

8-Bit

17

× 40ns + 127 × 322.6ns = 41.7μs

12-Bit

25

× 40ns + 148 × 645.2ns = 96.5μs

(1)

8-bit mode cycle time is calculated based on SDO-adjusted output mode.

(2)

CCLK period used for calculation is worst-case at 1.2V supply, 322.6ns.

28

Copyright

2011, Texas Instruments Incorporated

相關PDF資料 |

PDF描述 |

|---|---|

| TSC2046EIPWG4 | SPECIALTY CONSUMER CIRCUIT, PDSO16 |

| TSC2046IGQCR | SPECIALTY CONSUMER CIRCUIT, PBGA48 |

| TSC2046IPWR | SPECIALTY CONSUMER CIRCUIT, PDSO16 |

| TSC2046IPW | SPECIALTY CONSUMER CIRCUIT, PDSO16 |

| TSC2046IRGVR | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSC2011 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Nanopower, 4-Wire Resistive Touch and Haptic Controller with I2Ca?¢ Serial Interface |

| TSC2011IRTJR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Nanopower, 4-Wire Resistive Touch and Haptic Controller with I2Ca?¢ Serial Interface |

| TSC2011IRTJT | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Nanopower, 4-Wire Resistive Touch and Haptic Controller with I2Ca?¢ Serial Interface |

| TSC2011IYZKR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Nanopower, 4-Wire Resistive Touch and Haptic Controller with I2Ca?¢ Serial Interface |

| TSC2011IYZKT | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Nanopower, 4-Wire Resistive Touch and Haptic Controller with I2Ca?¢ Serial Interface |

發布緊急采購,3分鐘左右您將得到回復。