- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373914 > AD7707BR (ANALOG DEVICES INC) 3 V/5 V, +-10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC PDF資料下載

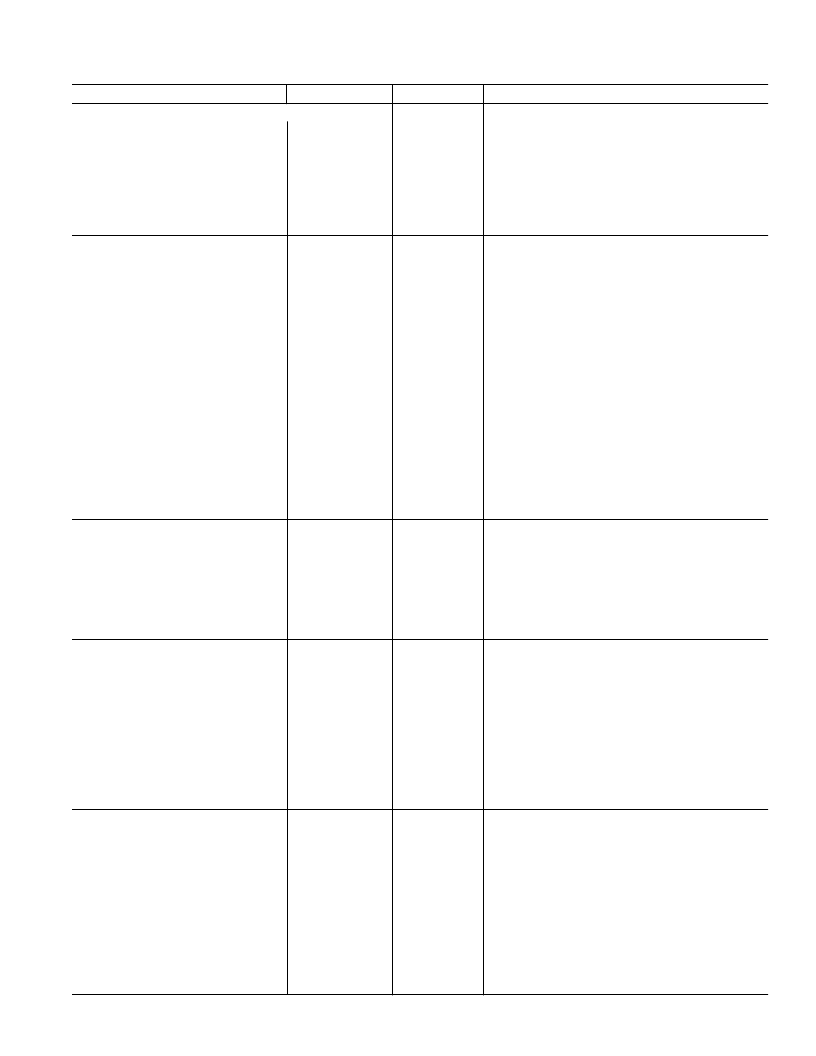

參數(shù)資料

| 型號: | AD7707BR |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 3 V/5 V, +-10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC |

| 中文描述: | 3-CH 16-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO20 |

| 封裝: | 0.300 INCH, SOIC-20 |

| 文件頁數(shù): | 3/40頁 |

| 文件大小: | 316K |

| 代理商: | AD7707BR |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

REV. A

–3–

AD7707

Parameter

B Version

1

Units

Conditions/Comments

HIGH LEVEL ANALOG INPUT CHANNEL (AIN3)

AIN3 Voltage Range

AIN3 is with respect to HICOM.

+10

–10

78

78

GAIN

×

f

CLKIN

/64

f

CLKIN

/8

27

10

0 V/AV

DD

V max

V min

dB typ

dB typ

Normal Mode 50 Hz Rejection

Normal Mode 60 Hz Rejection

AIN3 Input Sampling Rate, f

S

For Filter Notches of 10 Hz, 25 Hz, 50 Hz,

±

0.02

×

f

NOTCH

For Filter Notches of 10 Hz, 20 Hz, 60 Hz,

±

0.02

×

f

NOTCH

For Gains of 1 to 4

For Gains of 8 to 128

Typically 30 k

±

10%; Typical Resistor Tempco is –30ppm/

°

C

AIN3 Input Impedance

2

AIN3 Sampling Capacitance

2

VBIAS Input Range

k

min

pF max

V min/max

Typically = REFIN(+) = 2.5 V

LOGIC INPUTS

Input Current

All Inputs Except MCLK IN

MCLK

All Inputs Except SCLK and MCLK IN

V

INL

, Input Low Voltage

±

1

±

10

μ

A max

μ

A max

Typically

±

20 nA

Typically

±

2

μ

A

0.8

0.4

2.0

V max

V max

V min

DV

DD

= 5 V

DV

DD

= 3 V

DV

DD

= 3 V and 5 V

DV

DD

= 5 V Nominal

V

INH

, Input High Voltage

SCLK Only (Schmitt Triggered Input)

V

T+

V

T–

V

– V

SCLK Only (Schmitt Triggered Input)

V

T+

V

T–

V

– V

MCLK IN Only

V

INL

, Input Low Voltage

V

INH

, Input High Voltage

MCLK IN Only

V

INL

, Input Low Voltage

V

INH

, Input High Voltage

1.4/3

0.8/1.4

0.4/0.8

V min/V max

V min/V max

V min/V max

DV

DD

= 3 V Nominal

1/2.5

0.4/1.1

0.375/0.8

V min/V max

V min/V max

V min/V max

DV

DD

= 5 V Nominal

0.8

3.5

V max

V min

DV

DD

= 3 V Nominal

0.4

2.5

V max

V min

LOGIC OUTPUTS (Including MCLK OUT)

V

OL

, Output Low Voltage

0.4

0.4

4

DV

DD

– 0.6

±

10

9

Binary

Offset Binary

V max

V max

V min

V min

μ

A max

pF typ

I

SINK

= 800

μ

A Except for MCLK OUT.

13

DV

DD

= 5 V

I

SINK

= 100

μ

A Except for MCLK OUT.

13

DV

DD

= 3 V

I

SOURCE

= 200

μ

A Except for MCLK OUT.

13

DV

DD

= 5 V

I

SOURCE

= 100

μ

A Except for MCLK OUT.

13

DV

DD

= 3 V

V

OH

, Output High Voltage

Floating State Leakage Current

Floating State Output Capacitance

14

Data Output Coding

Unipolar Mode

Bipolar Mode

SYSTEM CALIBRATION

Low Level Input Channels (AIN1 and AIN2)

Positive Full-Scale Calibration Limit

15

Negative Full-Scale Calibration Limit

15

Offset Calibration Limit

16

Input Span

16

(1.05

×

V

REF

)/GAIN

– (1.05

×

V

REF

)/GAIN V max

– (1.05

×

V

REF

)/GAIN V max

(0.8

×

V

REF

)/GAIN

(2.1

×

V

REF

)/GAIN

V max

GAIN Is The Selected PGA Gain (1 to 128)

GAIN Is The Selected PGA Gain (1 to 128)

GAIN Is The Selected PGA Gain (1 to 128)

GAIN Is The Selected PGA Gain (1 to 128)

GAIN Is The Selected PGA Gain (1 to 128)

V min

V max

High Level Input Channels (AIN3)

Positive Full-Scale Calibration Limit

15

Negative Full-Scale Calibration Limit

15

Offset Calibration Limit

16

Input Span

16

(8.4

×

V

REF

)/GAIN

– (8.4

×

V

REF

)/GAIN

– (8.4

×

V

REF

)/GAIN

(6.4

×

V

REF

)/GAIN

(16.8

×

V

REF

)/GAIN

V max

V max

V max

V min

V max

GAIN Is The Selected PGA Gain (1 to 128)

GAIN Is The Selected PGA Gain (1 to 128)

GAIN Is The Selected PGA Gain (1 to 128)

GAIN Is The Selected PGA Gain (1 to 128)

GAIN Is The Selected PGA Gain (1 to 128)

POWER REQUIREMENTS

Power Supply Voltages

AV

DD

Voltage

+2.7 to +3.3 or

+4.75 to +5.25

+2.7 to +5.25

V

V

For Specified Performance

For Specified Performance

DV

DD

Voltage

Power Supply Currents

AV

DD

Current

AV

= 3V or 5V. Gain = 1 to 4

Typically 0.22 mA. BUF = 0. f

CLK

IN

= 1 MHz

or 2.4576MHz

Typically 0.45 mA. BUF = 1. f

CLK

IN

= 1 MHz

or 2.4576 MHz

AV

= 3 V or 5V. Gain = 8 to 128

Typically 0.38mA. BUF = 0. f

CLK

IN

= 2.4576MHz

Typically 0.81mA. BUF = 1. f

CLK

IN

= 2.4576MHz

0.27

mA max

0.6

mA max

0.5

1.1

mA max

mA max

相關PDF資料 |

PDF描述 |

|---|---|

| AD7707BRU | 3 V/5 V, +-10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC |

| AD7707 | ECONOLINE: REC2.2-S_DR/H1 - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- UL94V-0 Package Material- Continuous Short Circiut Protection- Internal SMD design- 100% Burned In- Efficiency to 75% |

| AD7707EB | 3 V/5 V 610 V Input Range 1 mW 3-Channel 16-Bit Sigma-Delta ADC(316.51 k) |

| AD7708BR | Shaft; Style: 2 - light; Applicable Model: LE-P / LEL-W |

| AD7708BRU | 8-/10-Channel, Low Voltage, Low Power, ADCs |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD7707BR-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20SOIC W - Tape and Reel |

| AD7707BR-REEL7 | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20SOIC W - Tape and Reel |

| AD7707BRU | 功能描述:IC ADC 16BIT 3CH 20-TSSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉換器 系列:- 標準包裝:1,000 系列:- 位數(shù):12 采樣率(每秒):300k 數(shù)據(jù)接口:并聯(lián) 轉換器數(shù)目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數(shù)目和類型:1 個單端,單極;1 個單端,雙極 |

| AD7707BRU-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin TSSOP T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20TSSOP - Tape and Reel |

| AD7707BRU-REEL7 | 功能描述:IC ADC 16BIT 3CH 20-TSSOP T/R RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉換器 系列:- 標準包裝:1,000 系列:- 位數(shù):16 采樣率(每秒):45k 數(shù)據(jù)接口:串行 轉換器數(shù)目:2 功率耗散(最大):315mW 電壓電源:模擬和數(shù)字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數(shù)目和類型:2 個單端,單極 |

發(fā)布緊急采購,3分鐘左右您將得到回復。