- 您現在的位置:買賣IC網 > PDF目錄373914 > AD7707BR (ANALOG DEVICES INC) 3 V/5 V, +-10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC PDF資料下載

參數資料

| 型號: | AD7707BR |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 3 V/5 V, +-10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC |

| 中文描述: | 3-CH 16-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO20 |

| 封裝: | 0.300 INCH, SOIC-20 |

| 文件頁數: | 5/40頁 |

| 文件大小: | 316K |

| 代理商: | AD7707BR |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

REV. A

AD7707

–5–

TIMING CHARACTERISTICS

1, 2

Limit at

T

MIN

, T

MAX

(B Version)

Parameter

Units

Conditions/Comments

f

CLKIN3, 4

400

5

0.4

×

t

CLKIN

0.4

×

t

CLKIN

500

×

t

CLKIN

100

kHz min

MHz max

ns min

ns min

ns nom

ns min

Master Clock Frequency: Crystal Oscillator or Externally Supplied for

Specified Performance

Master Clock Input Low Time. t

CLKIN

= 1/f

CLKIN

Master Clock Input High Time

DRDY

High Time

RESET

Pulsewidth

t

CLKIN

LO

t

CLKIN

HI

t

1

t

2

Read Operation

t

3

t

4

t

55

0

120

0

80

100

100

100

0

10

60

100

100

ns min

ns min

ns min

ns max

ns max

ns min

ns min

ns min

ns min

ns max

ns max

ns max

DRDY

to

CS

Setup Time

CS

Falling Edge to SCLK Rising Edge Setup Time

SCLK Falling Edge to Data Valid Delay

DV

DD

= +5V

DV

DD

= +3.0V

SCLK High Pulsewidth

SCLK Low Pulsewidth

CS

Rising Edge to SCLK Rising Edge Hold Time

Bus Relinquish Time after SCLK Rising Edge

DV

DD

= +5V

DV

DD

= +3.0V

SCLK Falling Edge to

DRDY

High

7

t

6

t

7

t

8

t

96

t

10

Write Operation

t

11

t

12

t

13

t

14

t

15

t

16

120

30

20

100

100

0

ns min

ns min

ns min

ns min

ns min

ns min

CS

Falling Edge to SCLK Rising Edge Setup Time

Data Valid to SCLK Rising Edge Setup Time

Data Valid to SCLK Rising Edge Hold Time

SCLK High Pulsewidth

SCLK Low Pulsewidth

CS

Rising Edge to SCLK Rising Edge Hold Time

NOTES

1

Sample tested at +25

°

C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of DV

DD

) and timed from a voltage level of 1.6 V.

2

See Figures 16 and 17.

3

f

CLKIN

Duty Cycle range is 45% to 55%. f

CLKIN

must be supplied whenever the AD7707 is not in Standby mode. If no clock is present in this case, the device can

draw higher current than specified and possibly become uncalibrated.

4

The AD7707 is production tested with f

CLKIN

at 2.4576MHz (1MHz for some I

DD

tests). It is guaranteed by characterization to operate at 400kHz.

5

These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross the V

OL

or V

OH

limits.

6

These numbers are derived from the measured time taken by the data output to change 0.5V when loaded with the circuit of Figure 1. The measured number is then

extrapolated back to remove effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus

relinquish times of the part and as such are independent of external bus loading capacitances.

7

DRDY

returns high after the first read from the device after an output update. The same data can be read again, if required, while

DRDY

is high, although care

should be taken that subsequent reads do not occur close to the next output update.

TO OUTPUT

PIN

50pF

I

SINK

(800

m

A AT V

DD

= +5V

100

m

A AT V

DD

= +3V)

+1.6V

I

SOURCE

(200

m

A AT V

DD

= +5V

100

m

A AT V

DD

= +3V)

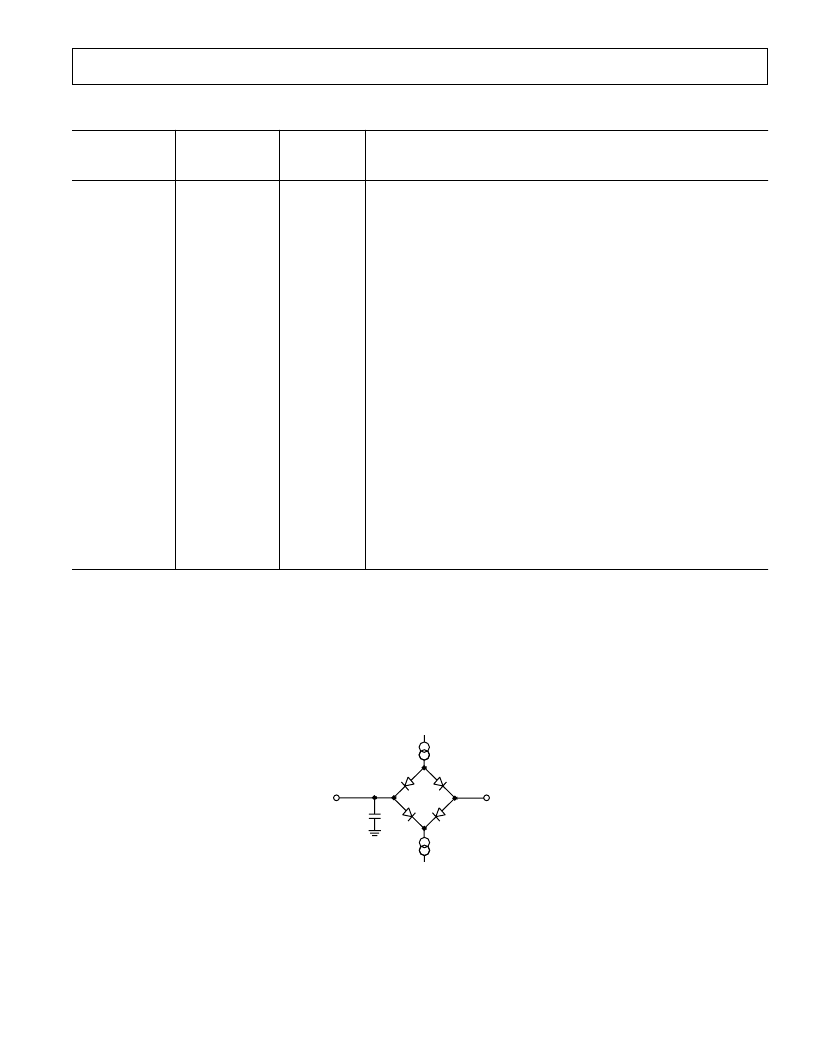

Figure 1. Load Circuit for Access Time and Bus Relinquish Time

(AV

DD

= DV

DD

= +2.7 V TO +5.25 V, AGND = DGND = 0 V; f

CLKIN

= 2.4576 MHz; Input

Logic = 0, Logic 1 = DV

DD

unless otherwise noted.)

相關PDF資料 |

PDF描述 |

|---|---|

| AD7707BRU | 3 V/5 V, +-10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC |

| AD7707 | ECONOLINE: REC2.2-S_DR/H1 - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- UL94V-0 Package Material- Continuous Short Circiut Protection- Internal SMD design- 100% Burned In- Efficiency to 75% |

| AD7707EB | 3 V/5 V 610 V Input Range 1 mW 3-Channel 16-Bit Sigma-Delta ADC(316.51 k) |

| AD7708BR | Shaft; Style: 2 - light; Applicable Model: LE-P / LEL-W |

| AD7708BRU | 8-/10-Channel, Low Voltage, Low Power, ADCs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7707BR-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20SOIC W - Tape and Reel |

| AD7707BR-REEL7 | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20SOIC W - Tape and Reel |

| AD7707BRU | 功能描述:IC ADC 16BIT 3CH 20-TSSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:12 采樣率(每秒):300k 數據接口:并聯 轉換器數目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數目和類型:1 個單端,單極;1 個單端,雙極 |

| AD7707BRU-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin TSSOP T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20TSSOP - Tape and Reel |

| AD7707BRU-REEL7 | 功能描述:IC ADC 16BIT 3CH 20-TSSOP T/R RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

發布緊急采購,3分鐘左右您將得到回復。