- 您現在的位置:買賣IC網 > PDF目錄373916 > AD7760BCP (ANALOG DEVICES INC) 2.5 MSPS, 20-Bit ADC PDF資料下載

參數資料

| 型號: | AD7760BCP |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 2.5 MSPS, 20-Bit ADC |

| 中文描述: | 1-CH 20-BIT DELTA-SIGMA ADC, PARALLEL ACCESS, QCC48 |

| 封裝: | LFCSP-48 |

| 文件頁數: | 12/22頁 |

| 文件大小: | 868K |

| 代理商: | AD7760BCP |

AD7760

Preliminary Technical Data

THEORY OF OPERATION

The AD7760 employs a sigma-delta conversion technique to

convert the analog input into an equivalent digital word. The

modulator samples the input waveform and outputs an

equivalent digital word to the digital filter at a rate equal to I

CLK

.

Rev. PrN | Page 12 of 22

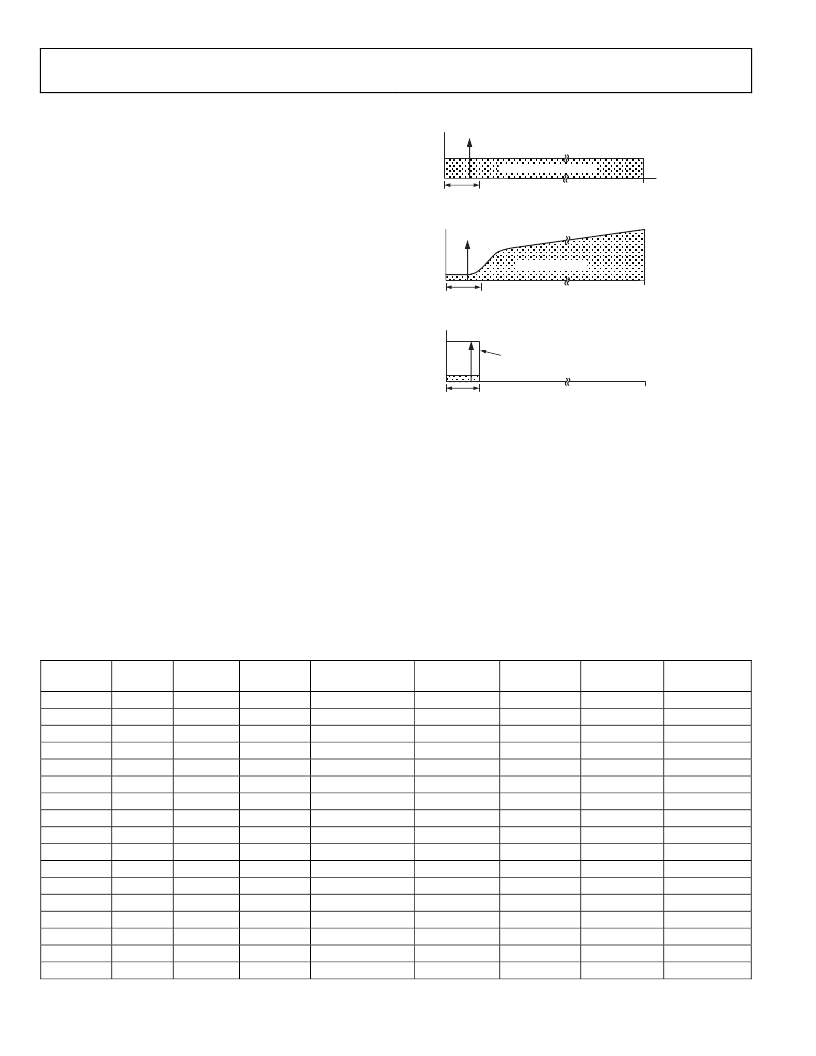

Due to the high over-sampling rate, which spreads the

quantization noise from 0 to

f

ICLK

, the noise energy contained in

the band of interest is reduced (Figure 13a). To further reduce

the quantization noise, a high order modulator is employed to

shape the noise spectrum; so that most of the noise energy is

shifted out of the band of interest (Figure 13b).

The digital filtering which follows the modulator removes the

large out-of-band quantization noise (Figure 13c) while also

reducing the data rate from

f

ICLK

at the input of the filter to

f

ICLK

/8

or less at the output of the filter, depending on the decimation

rate used.

Digital filtering has certain advantages over analog filtering. It

does not introduce significant noise or distortion and can be

made perfectly linear phase.

The AD7760 employs three Finite Impulse Response (FIR)

filters in series. By using different combinations of decimation

ratios and filter selection and bypassing, data can be obtained

from the AD7760 at a large range of data rates. Multi-bit data

from the modulator can be obtained at a rate of 20MHz. The

first filter receives data from the modulator at 20MHz where it

is decimated by four to output data at 5MHz. This partially

filtered data can also be output at this stage. The second filter

allows the decimation rate to be chosen from 2x to 32x or to be

Table 5. Configuration With Default Filter

ICLK

Frequency

20 MHz

Bypassed

Bypassed

20 MHz

4x

Bypassed

20 MHz

4x

Bypassed

20 MHz

4x

2x

20 MHz

4x

2x

20 MHz

4x

4x

20 MHz

4x

4x

20 MHz

4x

8x

20 MHz

4x

8x

20 MHz

4x

16x

20 MHz

4x

16x

20 MHz

4x

32x

20 MHz

4x

32x

12.288MHz

4x

8x

12.288MHz

4x

16x

12.288MHz

4x

32x

12.288MHz

4x

32x

!

"#

$%

&%

'%

Figure 13. Sigma-Delta ADC

completely bypassed. The third filter has a fixed decimation rate

of 2x and is user programmable as well as having a default

configuration. It is described in detail in the Programmable FIR

Filter Section. This filter can also be bypassed. Table X below

shows some characteristics of the default filter. The group delay

of the filter is defined to be the delay to the centre of the

impulse response and is equal to the computation + filter delays.

The delay until valid data is available (the DVALID status bit is

set) is equal to 2x the filter delay + the computation delay.

Filter 1

Filter 2

Filter 3

Data State

Computation

Delay

0

0.325

1.075

1.35

1.625

1.725

1.775

2.6

2.25

4.175

3.1

7.325

4.65

3.66

5.05

11.92

7.57

Filter Delay

Passband

Bandwidth

(10 MHz)

1.35 MHz

1 MHz

562.5 kHz

500 kHz

281.25 kHz

250 kHz

140.625 kHz

125 kHz

70.3125 kHz

62.5 kHz

35.156 kHz

31.25 kHz

76.8 kHz

38.4 kHz

21.6 kHz

19.2 kHz

Output Data

Rate (ODR)

20 MHz

5 MHz

2.5 MHz

2.5 MHz

1.25 MHz

1.25 MHz

625 kHz

625 kHz

312.5 kHz

312.5 kHz

156.25 kHz

156.25 kHz

78.125 kHz

192 kHz

96 kHz

96 kHz

48 kHz

Bypassed

Bypassed

2x

Bypassed

2x

Bypassed

2x

Bypassed

2x

Bypassed

2x

Bypassed

2x

2x

2x

Bypassed

2x

Unfiltered

Partially Filtered

Fully Filtered

Partially Filtered

Fully Filtered

Partially Filtered

Fully Filtered

Partially Filtered

Fully Filtered

Partially Filtered

Fully Filtered

Partially Filtered

Fully Filtered

Fully Filtered

Fully Filtered

Partially Filtered

Fully Filtered

0

1.2μS

10.8μS

3.6μS

22.8μS

6μS

44.4μS

10.8μS

87.6μS

20.4μS

174μS

39.6μS

346.8μS

142.6μS

283.2μS

64.45μS

564.5μS

相關PDF資料 |

PDF描述 |

|---|---|

| AD7760BSV | 2.5 MSPS, 20-Bit ADC |

| AD7769 | LC2MOS Analog I/O Port |

| AD7769AN | LC2MOS Analog I/O Port |

| AD7769AP | LC2MOS Analog I/O Port |

| AD7769JN | LC2MOS Analog I/O Port |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7760BCPZ | 制造商:Analog Devices 功能描述:2.5MSPS 18/20 BIT SIGMA DELTA ADC - Bulk |

| AD7760BST | 制造商:Analog Devices 功能描述:2.5MSPS 18/20 BIT SIGMA DELTA ADC - Bulk |

| AD7760BSV | 制造商:AD 制造商全稱:Analog Devices 功能描述:2.5 MSPS, 20-Bit ADC |

| AD7760BSVZ | 功能描述:IC ADC 24BIT 2.5MSPS 64TQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 其它有關文件:TSA1204 View All Specifications 標準包裝:1 系列:- 位數:12 采樣率(每秒):20M 數據接口:并聯 轉換器數目:2 功率耗散(最大):155mW 電壓電源:模擬和數字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應商設備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數目和類型:4 個單端,單極;2 個差分,單極 產品目錄頁面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

| AD7760BSVZ-REEL | 功能描述:IC ADC 24BIT 2.5MSPS 64TQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

發布緊急采購,3分鐘左右您將得到回復。